18-74 Vol. 3B

PERFORMANCE MONITORING

18.13.1 Processor Event Based Sampling (PEBS) Facility

The PEBS facility in the 6th Generation Intel Core processor provides a number enhancement relative to PEBS in

processors based on Haswell/Broadwell microarchitectures. The key components and differences of PEBS facility

relative to Haswell/Broadwell microarchitecture is summarized in Table 18-54.

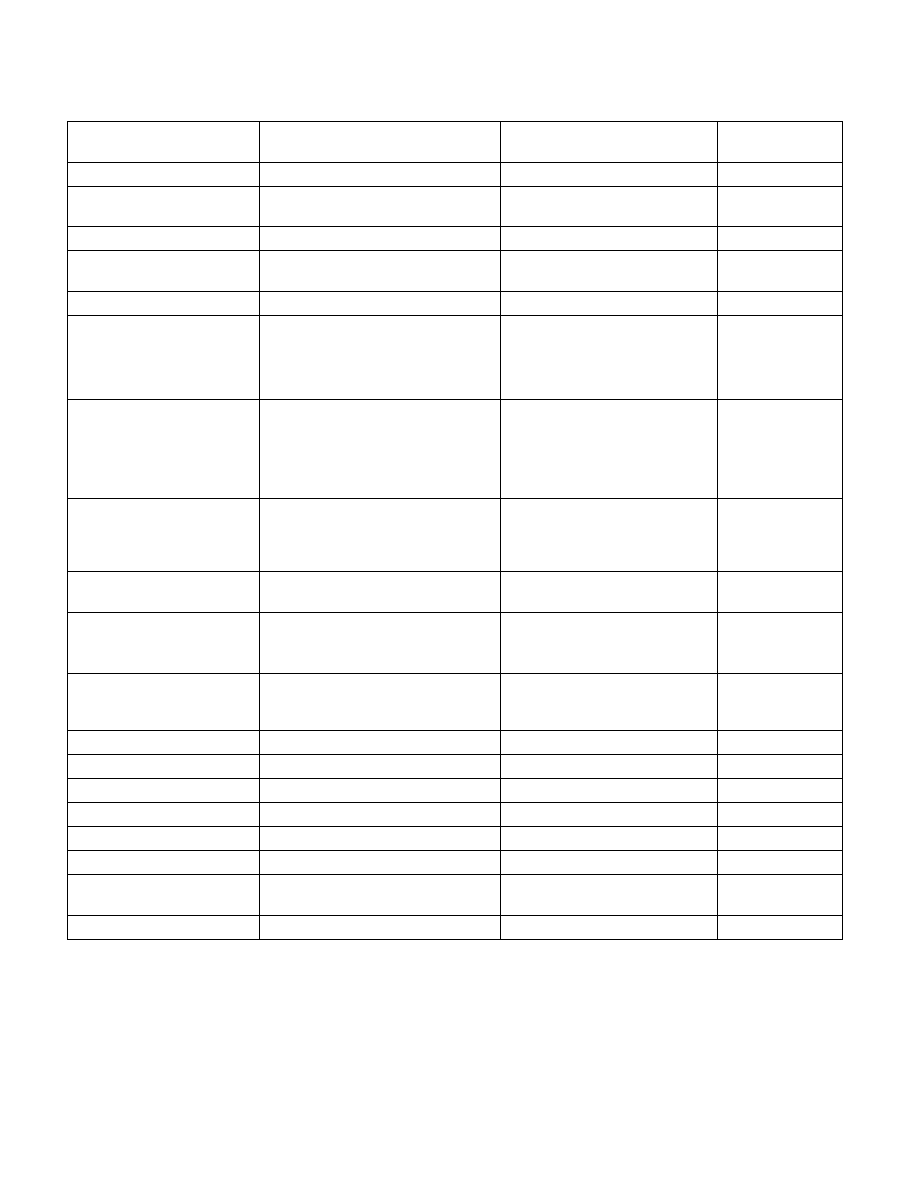

Table 18-53. Core PMU Comparison

Box

Intel® microarchitecture code name

Skylake

Intel® microarchitecture code

name Haswell and Broadwell

Comment

# of Fixed counters per thread

3

3

# of general-purpose counters

per core

8

8

Counter width (R,W)

R:48, W: 32/48

R:48, W: 32/48

See Section 18.2.2.

# of programmable counters

per thread

4 or (8 if a core not shared by two

threads)

4 or (8 if a core not shared by two

threads)

CPUID enumerates

# of counters.

Architectural Perfmon version

4

3

See Section 18.2.4

PMI Overhead Mitigation

• Freeze_Perfmon_on_PMI with

streamlined semantics.

• Freeze_on_LBR with streamlined

semantics.

• Freeze_while_SMM.

• Freeze_Perfmon_on_PMI with

legacy semantics.

• Freeze_on_LBR with legacy

semantics for branch profiling.

• Freeze_while_SMM.

See Section 17.4.7.

Legacy semantics

not supported with

version 4 or higher.

Counter and Buffer Overflow

Status Management

• Query via

IA32_PERF_GLOBAL_STATUS

• Reset via

IA32_PERF_GLOBAL_STATUS_RESET

• Set via

IA32_PERF_GLOBAL_STATUS_SET

• Query via

IA32_PERF_GLOBAL_STATUS

• Reset via

IA32_PERF_GLOBAL_OVF_CTRL

IA32_PERF_GLOBAL_STATUS

Indicators of

Overflow/Overhead/Interferen

ce

• Individual counter overflow

• PEBS buffer overflow

• ToPA buffer overflow

• CTR_Frz, LBR_Frz, ASCI

• Individual counter overflow

• PEBS buffer overflow

• ToPA buffer overflow (applicable

to Broadwell microarchitecture)

Enable control in

IA32_PERF_GLOBAL_STATUS

• CTR_Frz,

• LBR_Frz

NA

Perfmon Counter In-Use

Indicator

Query IA32_PERF_GLOBAL_INUSE

NA

See Section

Precise Events

IA32_PMC4-PMC7

do not support

PEBS.

PEBS for front end events

No

LBR Record Format Encoding

000101b

000100b

LBR Size

32 entries

16 entries

LBR Entry

From_IP/To_IP/LBR_Info triplet

From_IP/To_IP pair

LBR Timing

Yes

No

Call Stack Profiling

Yes, see Section 17.9

Use LBR facility

Off-core Response Event

MSR 1A6H and 1A7H; Extended request

and response types.

MSR 1A6H and 1A7H; Extended

request and response types.

Intel TSX support for Perfmon

See Section 18.11.5;

See Section 18.11.5;