Vol. 3B 17-31

DEBUG, BRANCH PROFILE, TSC, AND RESOURCE MONITORING FEATURES

17.10 LAST BRANCH, CALL STACK, INTERRUPT, AND EXCEPTION RECORDING

FOR PROCESSORS BASED ON SKYLAKE MICROARCHITECTURE

Processors based on the Skylake microarchitecture provide a number of enhancement with storing last branch

records:

•

enumeration of new LBR format: encoding 00101b in IA32_PERF_CAPABILITIES[5:0] is supported, see Section

17.4.8.1.

•

Each LBR stack entry consists of a triplets of MSRs:

— MSR_LASTBRANCH_x_FROM_IP, the layout is simplified, see Table 17-9.

— MSR_LASTBRANCH_x_TO_IP, the layout is the same as Table 17-9.

— MSR_LBR_INFO_x, stores branch prediction flag, TSX info, and elapsed cycle data.

•

Size of LBR stack increased to 32.

Processors based on the Skylake microarchitecture supports the same LBR filtering capabilities as described in

Table 17-13.

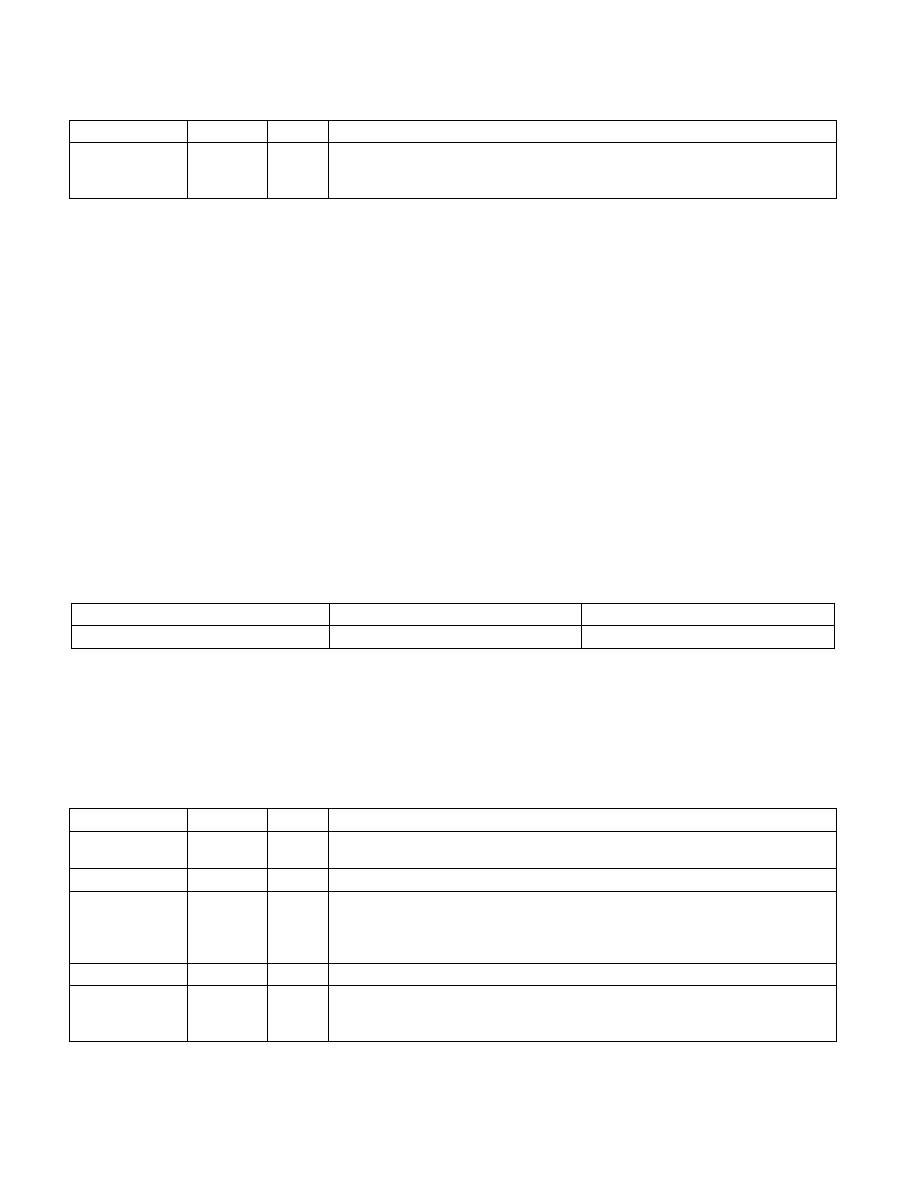

Table 17-15. LBR Stack Size and TOS Pointer Range

17.10.1 MSR_LBR_INFO_x

MSR

The layout of each MSR_LBR_INFO_x MSR is shown in Table 17-16.

MISPRED

63

R/O

When set, indicates either the target of the branch was mispredicted and/or the

direction (taken/non-taken) was mispredicted; otherwise, the target branch was

predicted.

DisplayFamily_DisplayModel

Size of LBR Stack

Range of TOS Pointer

06_4EH, 06_5EH

32

0 to 31

Table 17-16. MSR_LBR_INFO_x

Bit Field

Bit Offset

Access

Description

Cycle Count

(saturating)

15:0

R/O

Elapsed core clocks since last update to the LBR stack

Reserved

60:16

R/O

Reserved

TSX_ABORT

61

R/0

When set, indicates a TSX Abort entry

LBR_FROM: EIP at the time of the TSX Abort

LBR_TO: EIP of the start of HLE region OR

EIP of the RTM Abort Handler

IN_TSX

62

R/0

When set, indicates the entry occurred in a TSX region.

MISPRED

63

R/O

When set, indicates either the target of the branch was mispredicted and/or the

direction (taken/non-taken) was mispredicted; otherwise, the target branch was

predicted.

Table 17-14. MSR_LASTBRANCH_x_FROM_IP with TSX Information (Contd.)

Bit Field

Bit Offset

Access

Description