Vol. 3B 18-69

PERFORMANCE MONITORING

18.11.4.1 Off-core Response Performance Monitoring in Intel Xeon Processors E5 v3 Series

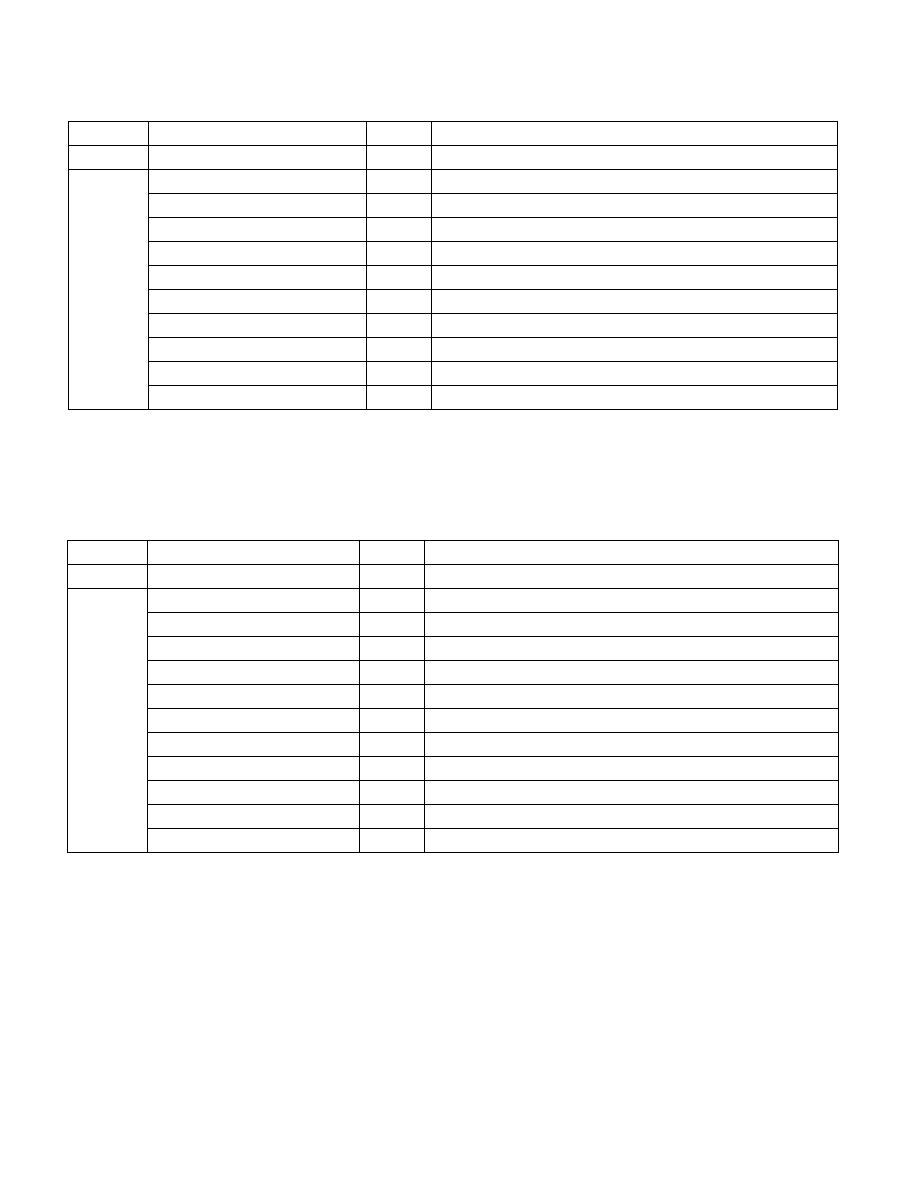

Table 18-48 lists the supplier information field that apply to Intel Xeon processor E5 v3 series (CPUID signature

06_3FH).

18.11.5 Performance Monitoring and Intel

┬о

TSX

Chapter 16 of Intel┬о 64 and IA-32 Architectures Software DeveloperтАЩs Manual, Volume 1 describes the details of

Intel┬о Transactional Synchronization Extensions (Intel TSX). This section describes performance monitoring

support for Intel TSX.

If a processor supports Intel TSX, the core PMU enhances itтАЩs IA32_PERFEVTSELx MSR with two additional bit fields

for event filtering. Support for Intel TSX is indicated by either (a) CPUID.(EAX=7, ECX=0):RTM[bit 11]=1, or (b) if

CPUID.07H.EBX.HLE [bit 4] = 1. The TSX-enhanced layout of IA32_PERFEVTSELx is shown in Figure 18-40. The

two additional bit fields are:

Table 18-49. MSR_OFFCORE_RSP_x Supplier Info Field Definition (CPUID Signature 06_45H)

Subtype

Bit Name

Offset

Description

Common

Any

16

(R/W). Catch all value for any response types.

Supplier

Info

NO_SUPP

17

(R/W). No Supplier Information available

L3_HITM

18

(R/W). M-state initial lookup stat in L3.

L3_HITE

19

(R/W). E-state

L3_HITS

20

(R/W). S-state

Reserved

21

Reserved

L4_HIT_LOCAL_L4

22

(R/W). L4 Cache

L4_HIT_REMOTE_HOP0_L4

23

(R/W). L4 Cache

L4_HIT_REMOTE_HOP1_L4

24

(R/W). L4 Cache

L4_HIT_REMOTE_HOP2P_L4

25

(R/W). L4 Cache

Reserved

30:26

Reserved

Table 18-50. MSR_OFFCORE_RSP_x Supplier Info Field Definition

Subtype

Bit Name

Offset

Description

Common

Any

16

(R/W). Catch all value for any response types.

Supplier

Info

NO_SUPP

17

(R/W). No Supplier Information available

L3_HITM

18

(R/W). M-state initial lookup stat in L3.

L3_HITE

19

(R/W). E-state

L3_HITS

20

(R/W). S-state

L3_HITF

21

(R/W). F-state

LOCAL

22

(R/W). Local DRAM Controller

Reserved

26:23

Reserved

L3_MISS_REMOTE_HOP0

27

(R/W). Hop 0 Remote supplier

L3_MISS_REMOTE_HOP1

28

(R/W). Hop 1 Remote supplier

L3_MISS_REMOTE_HOP2P

29

(R/W). Hop 2 or more Remote supplier

Reserved

30

Reserved