Vol. 3B 18-75

PERFORMANCE MONITORING

Only IA32_PMC0 through IA32_PMC3 support PEBS.

NOTES

Precise events are only valid when the following fields of IA32_PERFEVTSELx are all zero:

AnyThread, Edge, Invert, CMask.

In a PMU with PDIR capability, PEBS behavior is unpredictable if IA32_PERFEVTSELx or IA32_PMCx

is changed for a PEBS-enabled counter while an event is being counted. To avoid this, changes to

the programming or value of a PEBS-enabled counter should be performed when the counter is

disabled.

18.13.1.1 PEBS Data Format

The PEBS record format for the 6th generation Intel Core processor is reporting with encoding 0011b in

IA32_PERF_CAPABILITIES[11:8]. The lay out is shown in Table 18-55. The PEBS record format, along with

debug/store area storage format, does not change regardless of whether IA-32e mode is active or not.

CPUID.01H:ECX.DTES64[bit 2] reports whether the processor's DS storage format support is mode-independent.

When set, it uses 64-bit DS storage format.

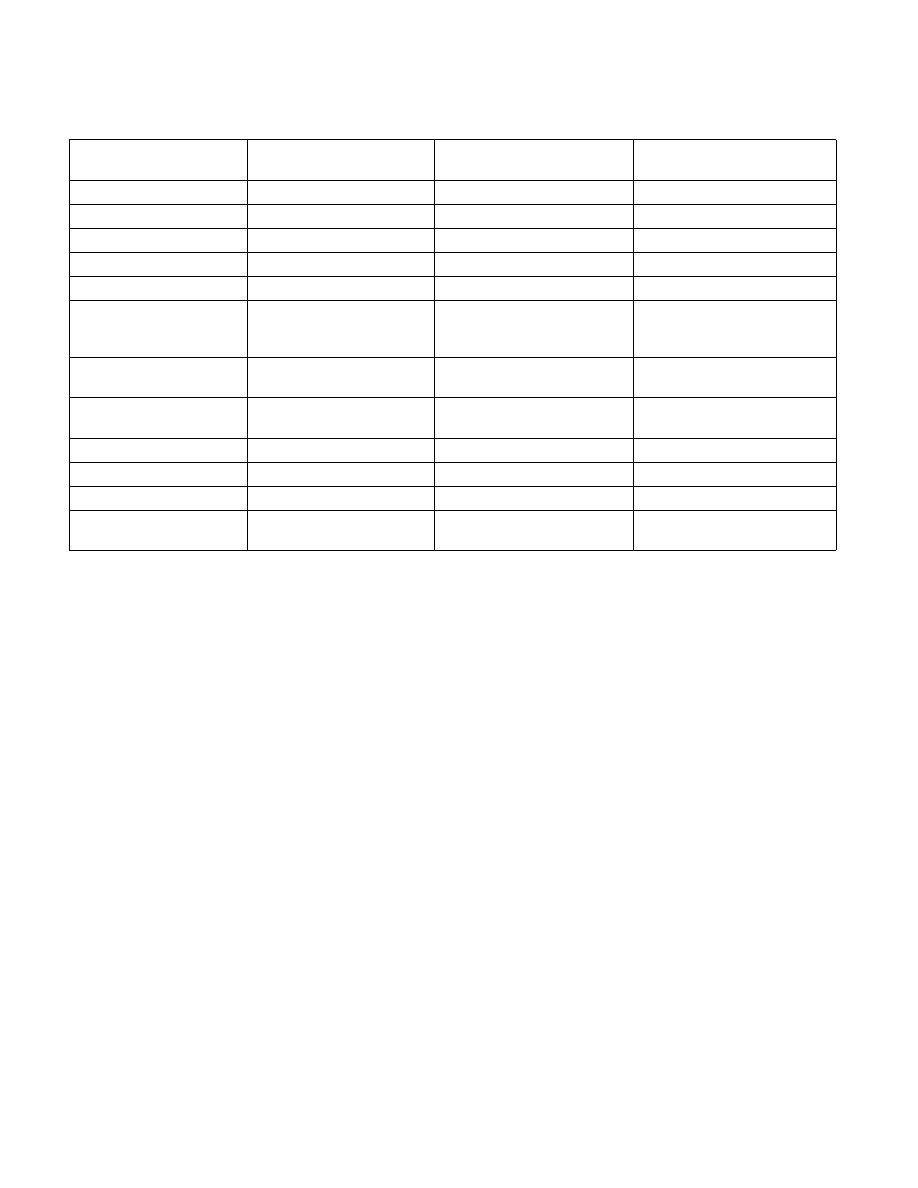

Table 18-54. PEBS Facility Comparison

Box

Intel® microarchitecture code

name Skylake

Intel® microarchitecture code

name Haswell and Broadwell

Comment

Valid IA32_PMCx

PMC0-PMC3

PMC0-PMC3

No PEBS on PMC4-PMC7.

PEBS Buffer Programming

Unchanged

IA32_PEBS_ENABLE Layout

PEBS-EventingIP

Yes

Yes

PEBS record format encoding 0011b

0010b

PEBS record layout

Table 18-55; enhanced fields

at offsets 98H- B8H; and TSC

record field at C0H.

Table 18-44; enhanced fields at

offsets 98H, A0H, A8H, B0H.

Multi-counter PEBS

resolution

PEBS record 90H resolves the

eventing counter overflow.

PEBS record 90H reflects

IA32_PERF_GLOBAL_STATUS.

Precise Events

See Table 18-56.

See Table 18-32.

IA32_PMC4-IA32_PMC7 do not

support PEBS.

PEBS-PDIR

Yes

Yes

IA32_PMC1 only.

PEBS-Load Latency

See Section 18.9.4.2.

Data Address Profiling

Yes

Yes

FrontEnd event support

FrontEnd_Retried event and

MSR_PEBS_FRONTEND.

No

IA32_PMC0-PMC3 only.