Vol. 3B 18-77

PERFORMANCE MONITORING

18.13.1.3 Data Address Profiling

The PEBS Data address profiling on the 6th generation Intel Core processor is largely unchanged from prior gener-

ation. When the DataLA facility is enabled, the relevant information written into a PEBS record affects entries at

offsets 98H, A0H and A8H, as shown in Table 18-46.

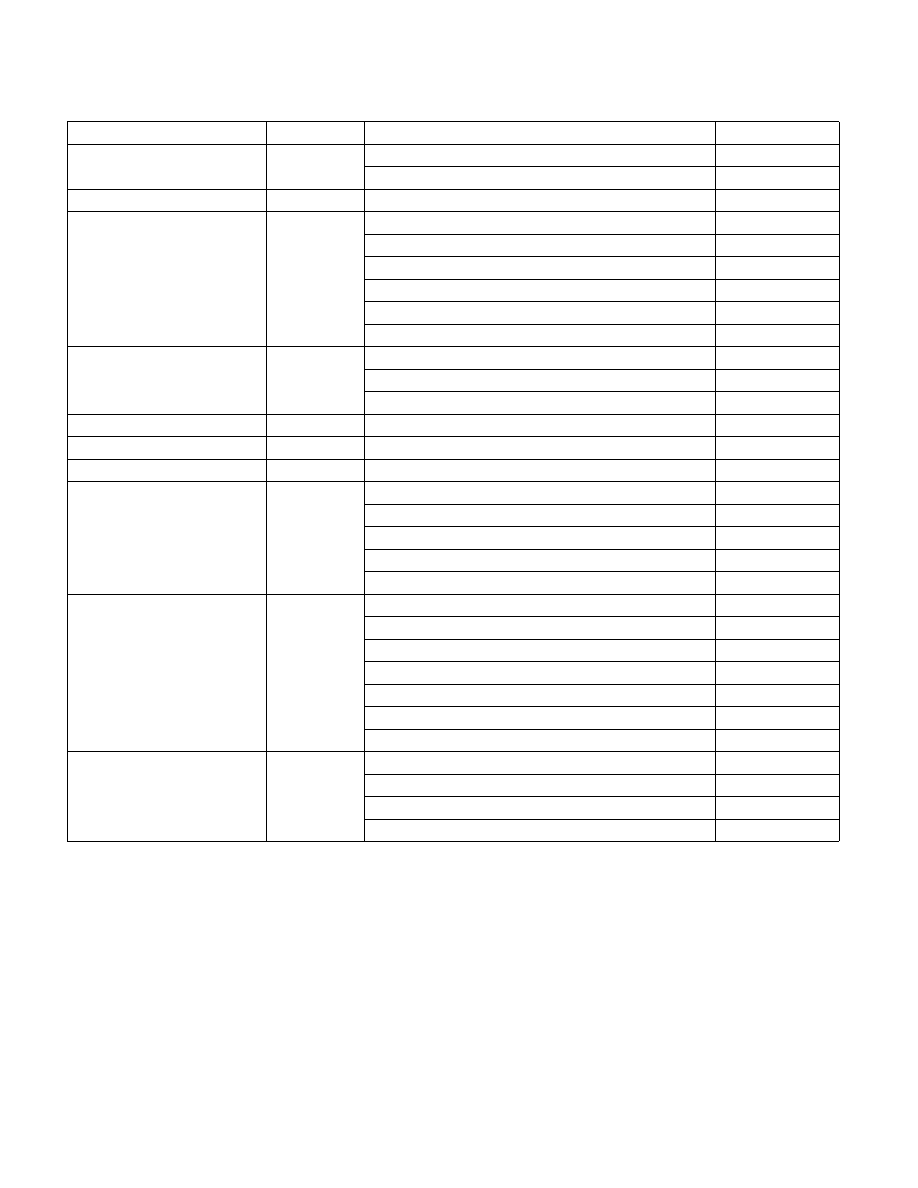

Table 18-56. Precise Events for the Skylake Microarchitecture

Event Name

Event Select

Sub-event

UMask

INST_RETIRED

C0H

PREC_DIST

1

01H

ALL_CYCLES

2

01H

OTHER_ASSISTS

C1H

ANY

3FH

BR_INST_RETIRED

C4H

CONDITIONAL

01H

NEAR_CALL

02H

ALL_BRANCHES

04H

NEAR_RETURN

08H

NEAR_TAKEN

20H

FAR_BRACHES

40H

BR_MISP_RETIRED

C5H

CONDITIONAL

01H

ALL_BRANCHES

04H

NEAR_TAKEN

20H

FRONTEND_RETIRED

C6H

<Programmable

3

>

01H

HLE_RETIRED

C8H

ABORTED

04H

RTM_RETIRED

C9H

ABORTED

04H

MEM_INST_RETIRED

2

D0H

LOCK_LOADS

21H

SPLIT_LOADS

41H

SPLIT_STORES

42H

ALL_LOADS

81H

ALL_STORES

82H

MEM_LOAD_RETIRED

4

D1H

L1_HIT

01H

L2_HIT

02H

L3_HIT

04H

L1_MISS

08H

L2_MISS

10H

L3_MISS

20H

HIT_LFB

40H

MEM_LOAD_L3_HIT_RETIRED

2

D2H

XSNP_MISS

01H

XSNP_HIT

02H

XSNP_HITM

04H

XSNP_NONE

08H

NOTES:

1. Only available on IA32_PMC1.

2. INST_RETIRED.ALL_CYCLES is configured with additional parameters of cmask = 10 and INV = 1

3. Subevents are specified using MSR_PEBS_FRONTEND, see Section 18.13.2

4. Instruction with at least one load uop experiencing the condition specified in the UMask.