Vol. 3B 18-55

PERFORMANCE MONITORING

18.9.4.2 Load Latency Performance Monitoring Facility

The load latency facility in Intel microarchitecture code name Sandy Bridge is similar to that in prior microarchitec-

ture. It provides software a means to characterize the average load latency to different levels of cache/memory

hierarchy. This facility requires processor supporting enhanced PEBS record format in the PEBS buffer, see

Table 18-23 and Section 18.9.4.1. This field measures the load latency from load's first dispatch of till final data

writeback from the memory subsystem. The latency is reported for retired demand load operations and in core

cycles (it accounts for re-dispatches).

To use this feature software must assure:

•

One of the IA32_PERFEVTSELx MSR is programmed to specify the event unit

MEM_TRANS_RETIRED, and the

LATENCY_ABOVE_THRESHOLD event mask must be specified (IA32_PerfEvtSelX[15:0] = 1CDH). The corre-

sponding counter IA32_PMCx will accumulate event counts for architecturally visible loads which exceed the

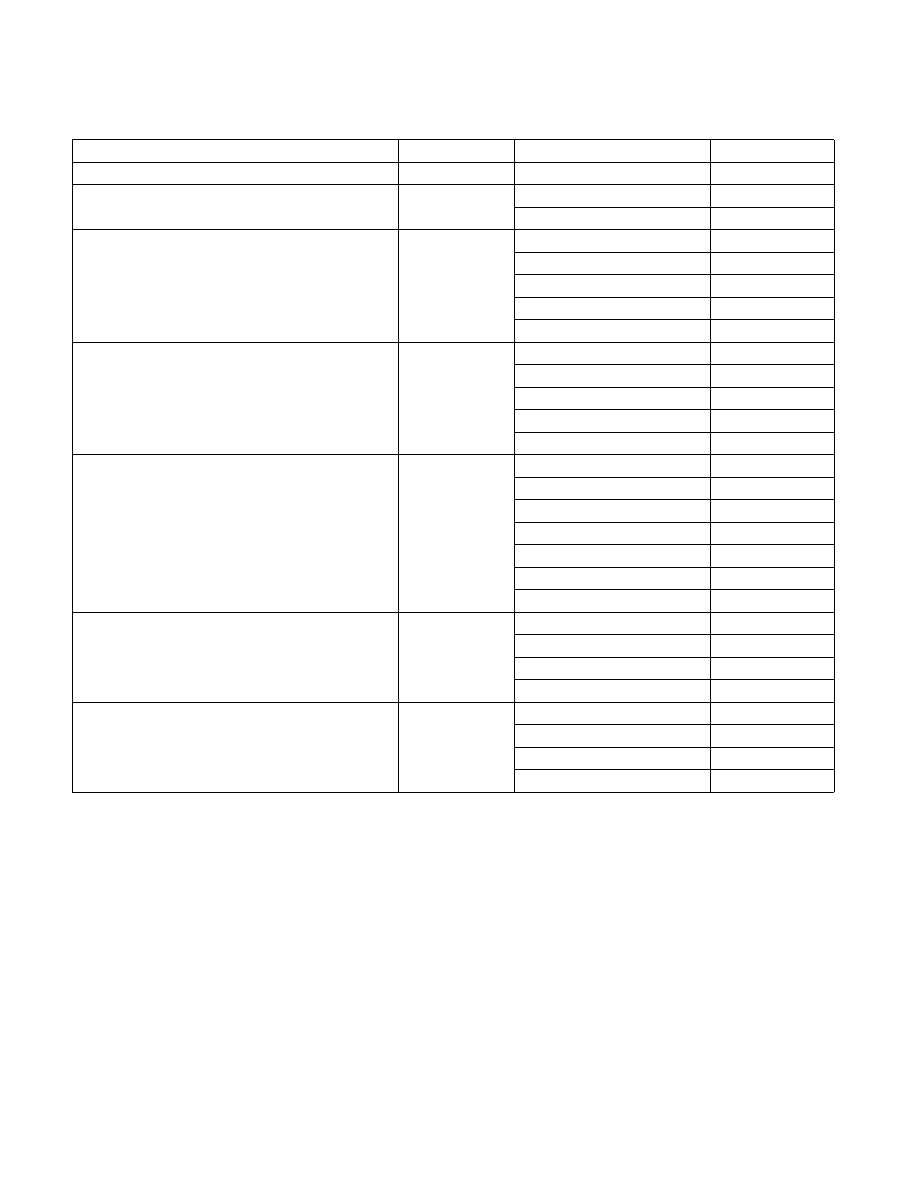

Table 18-32. PEBS Performance Events for Intel® Microarchitecture Code Name Sandy Bridge

Event Name

Event Select

Sub-event

UMask

INST_RETIRED

C0H

PREC_DIST

01H

1

NOTES:

1. Only available on IA32_PMC1.

UOPS_RETIRED

C2H

All

01H

Retire_Slots

02H

BR_INST_RETIRED

C4H

Conditional

01H

Near_Call

02H

All_branches

04H

Near_Return

08H

Near_Taken

20H

BR_MISP_RETIRED

C5H

Conditional

01H

Near_Call

02H

All_branches

04H

Not_Taken

10H

Taken

20H

MEM_UOPS_RETIRED

D0H

STLB_MISS_LOADS

11H

STLB_MISS_STORE

12H

LOCK_LOADS

21H

SPLIT_LOADS

41H

SPLIT_STORES

42H

ALL_LOADS

81H

ALL_STORES

82H

MEM_LOAD_UOPS_RETIRED

D1H

L1_Hit

01H

L2_Hit

02H

L3_Hit

04H

Hit_LFB

40H

MEM_LOAD_UOPS_LLC_HIT_RETIRED

D2H

XSNP_Miss

01H

XSNP_Hit

02H

XSNP_Hitm

04H

XSNP_None

08H