Vol. 3B 18-13

PERFORMANCE MONITORING

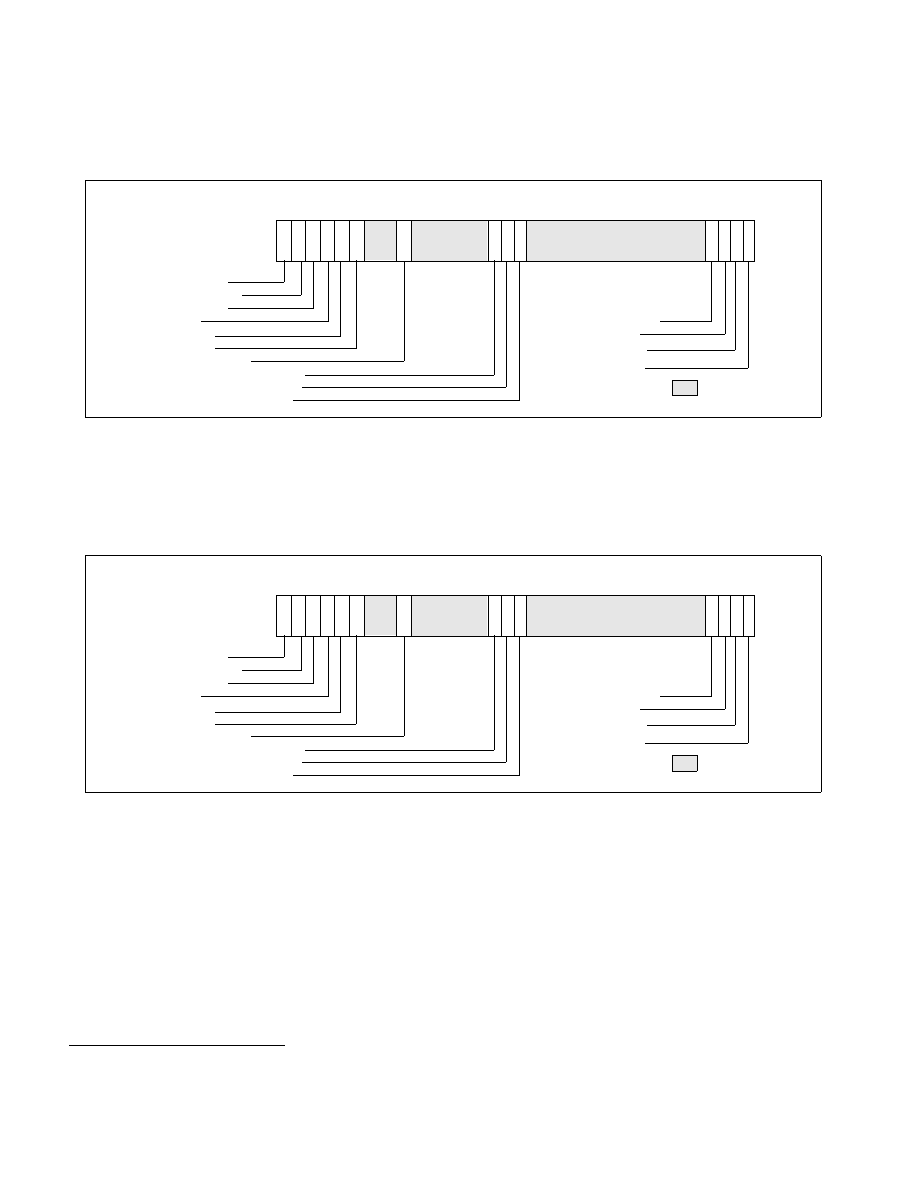

The address and the architecturally-defined bits of IA32_PERF_GLOBAL_OVF_CTRL is inherited by

IA32_PERF_GLOBAL_STATUS_RESET (see Figure 18-11). Further, IA32_PERF_GLOBAL_STATUS_RESET provides

additional bit fields to clear the new indicators in IA32_PERF_GLOBAL_STATUS described in Section 18.2.4.1.

The IA32_PERF_GLOBAL_STATUS_SET MSR is introduced with architectural performance monitoring version 4. It

allows software to set individual bits in IA32_PERF_GLOBAL_STATUS. The IA32_PERF_GLOBAL_STATUS_SET

interface can be used by a VMM to virtualize the state of IA32_PERF_GLOBAL_STATUS across VMs.

18.2.4.3 IA32_PERF_GLOBAL_INUSE MSR

In a contemporary software environment, multiple privileged service agents may wish to employ the processor’s

performance monitoring facilities. The IA32_MISC_ENABLES.PERFMON_AVAILABLE[bit 7] interface could not

serve the need of multiple agent adequately. A white paper, “Performance Monitoring Unit Sharing Guideline”

1

,

proposed a cooperative sharing protocol that is voluntary for participating software agents.

Architectural performance monitoring version 4 introduces a new MSR, IA32_PERF_GLOBAL_INUSE, that simplifies

the task of multiple cooperating agents to implement the sharing protocol.

The layout of IA32_PERF_GLOBAL_INUSE is shown in Figure 18-13.

Figure 18-11. IA32_PERF_GLOBAL_STATUS_RESET MSR and Architectural Perfmon Version 4

Figure 18-12. IA32_PERF_GLOBAL_STATUS_SET MSR and Architectural Perfmon Version 4

1. Available at http://www.intel.com/sdm

Reserved

62

Clr IA32_FIXED_CTR2 Ovf

Clr IA32_FIXED_CTR1 Ovf

Clr IA32_FIXED_CTR0 Ovf

Clr TraceToPAPMI

.. 1 0

Clr IA32_PMC0 Ovf

31

32

33

34

35

63

Clr CondChgd

Clr OvfDSBuffer

..

N

Clr ...................... Ovf

Clr IA32_PMC(N-1) Ovf

Clr OvfUncore

61

Clr IA32_PMC1 Ovf

60 59 58

55

Clr ASCI

Clr LBR_Frz

Clr CTR_Frz

Reserved

62

Set IA32_FIXED_CTR2 Ovf

Set IA32_FIXED_CTR1 Ovf

Set IA32_FIXED_CTR0 Ovf

Set TraceToPAPMI

.. 1 0

Set IA32_PMC0 Ovf

31

32

33

34

35

63

Set CondChgd

Set OvfDSBuffer

..

N

Set ...................... Ovf

Set IA32_PMC(N-1) Ovf

Set OvfUncore

61

Set IA32_PMC1 Ovf

60 59 58

55

Set ASCI

Set LBR_Frz

Set CTR_Frz