Vol. 3B 17-29

DEBUG, BRANCH PROFILE, TSC, AND RESOURCE MONITORING FEATURES

17.8

LAST BRANCH, INTERRUPT, AND EXCEPTION RECORDING FOR

PROCESSORS BASED ON INTEL

®

MICROARCHITECTURE CODE NAME

SANDY BRIDGE

Generally, all of the last branch record, interrupt and exception recording facility described in Section 17.7, “Last

Branch, Interrupt, and Exception Recording for Processors based on Intel® Microarchitecture code name

Nehalem”, apply to processors based on Intel microarchitecture code name Sandy Bridge. For processors based on

Intel microarchitecture code name Ivy Bridge, the same holds true.

One difference of note is that MSR_LBR_SELECT is shared between two logical processors in the same core. In Intel

microarchitecture code name Sandy Bridge, each logical processor has its own MSR_LBR_SELECT. The filtering

semantics for “Near_ind_jmp” and “Near_rel_jmp” has been enhanced, see Table 17-12.

17.9

LAST BRANCH, CALL STACK, INTERRUPT, AND EXCEPTION RECORDING

FOR PROCESSORS BASED ON HASWELL MICROARCHITECTURE

Generally, all of the last branch record, interrupt and exception recording facility described in Section 17.8, “Last

Branch, Interrupt, and Exception Recording for Processors based on Intel® Microarchitecture code name Sandy

Bridge”, apply to next generation processors based on Intel microarchitecture code name Haswell.

The LBR facility also supports an alternate capability to profile call stack profiles. Configuring the LBR facility to

conduct call stack profiling is by writing 1 to the MSR_LBR_SELECT.EN_CALLSTACK[bit 9]; see Table 17-13. If

MSR_LBR_SELECT.EN_CALLSTACK is clear, the LBR facility will capture branches normally as described in Section

17.8.

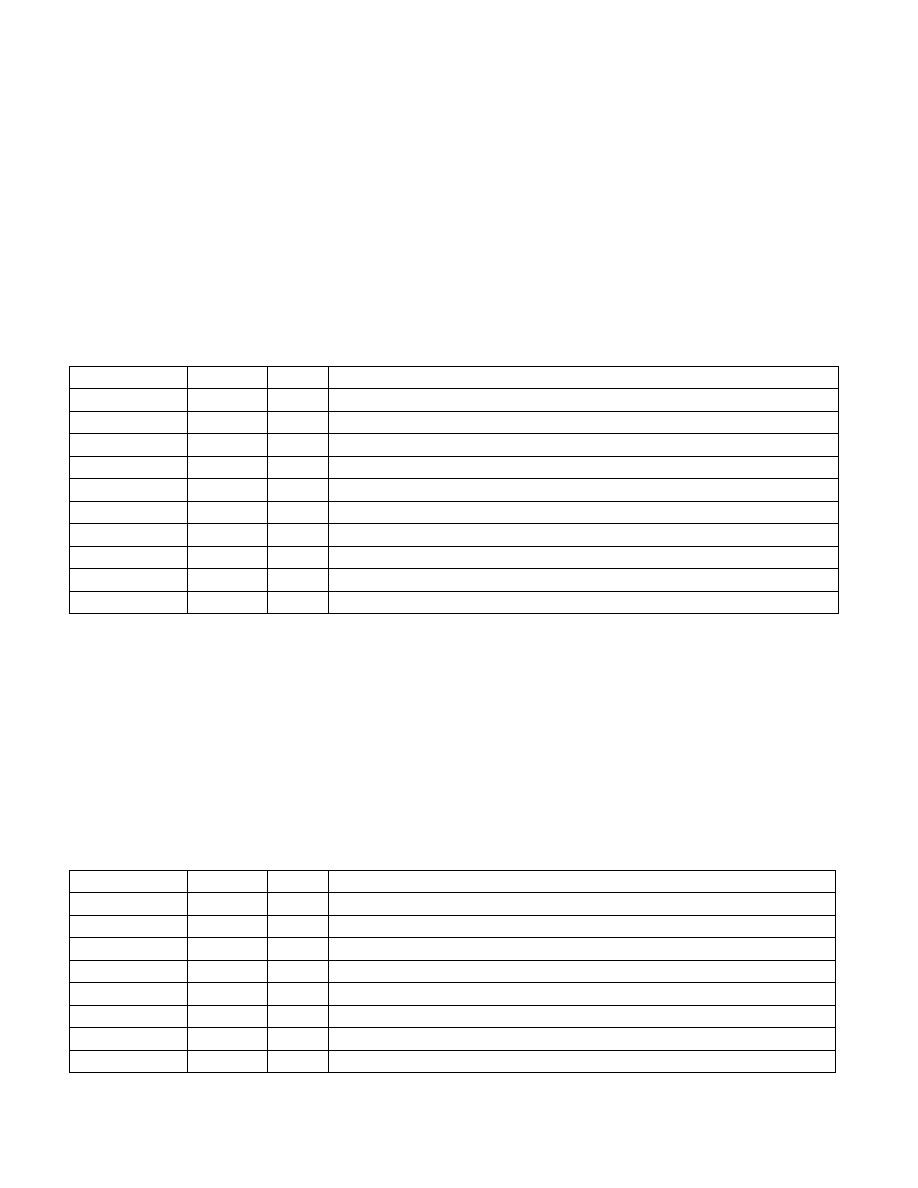

Table 17-12. MSR_LBR_SELECT for Intel® microarchitecture code name Sandy Bridge

Bit Field

Bit Offset

Access

Description

CPL_EQ_0

0

R/W

When set, do not capture branches occurring in ring 0

CPL_NEQ_0

1

R/W

When set, do not capture branches occurring in ring >0

JCC

2

R/W

When set, do not capture conditional branches

NEAR_REL_CALL

3

R/W

When set, do not capture near relative calls

NEAR_IND_CALL

4

R/W

When set, do not capture near indirect calls

NEAR_RET

5

R/W

When set, do not capture near returns

NEAR_IND_JMP

6

R/W

When set, do not capture near indirect jumps except near indirect calls and near returns

NEAR_REL_JMP

7

R/W

When set, do not capture near relative jumps except near relative calls.

FAR_BRANCH

8

R/W

When set, do not capture far branches

Reserved

63:9

Must be zero

Table 17-13. MSR_LBR_SELECT for Intel® microarchitecture code name Haswell

Bit Field

Bit Offset

Access

Description

CPL_EQ_0

0

R/W

When set, do not capture branches occurring in ring 0

CPL_NEQ_0

1

R/W

When set, do not capture branches occurring in ring >0

JCC

2

R/W

When set, do not capture conditional branches

NEAR_REL_CALL

3

R/W

When set, do not capture near relative calls

NEAR_IND_CALL

4

R/W

When set, do not capture near indirect calls

NEAR_RET

5

R/W

When set, do not capture near returns

NEAR_IND_JMP

6

R/W

When set, do not capture near indirect jumps except near indirect calls and near returns

NEAR_REL_JMP

7

R/W

When set, do not capture near relative jumps except near relative calls.