18-78 Vol. 3B

PERFORMANCE MONITORING

18.13.1.4 PEBS Facility for Front End Events

In the 6th generation Intel Core processor, the PEBS facility has been extended to allow capturing PEBS data for

some microarchitectural conditions related to front end events. The frontend microarchitectural conditions

supported by PEBS requires the following interfaces:

•

The IA32_PERFEVTSELx MSR must select “FrontEnd_Retired” (C6H) in the EventSelect field (bits 7:0) and

umask = 01H,

•

The “FRONTEND_RETIRED” event employs a new MSR, MSR_PEBS_FRONTEND, to specify the supported

frontend event details, see Table 18-58.

•

Program the PEBS_EN_PMCx field of IA32_PEBS_ENABLE MSR as required.

Note the AnyThread field of IA32_PERFEVTSELx is ignored by the processor for the “FRONTEND_RETIRED” event.

The sub-event encodings supported by MSR_PEBS_FRONTEND.EVTSEL is given in Table 18-58.

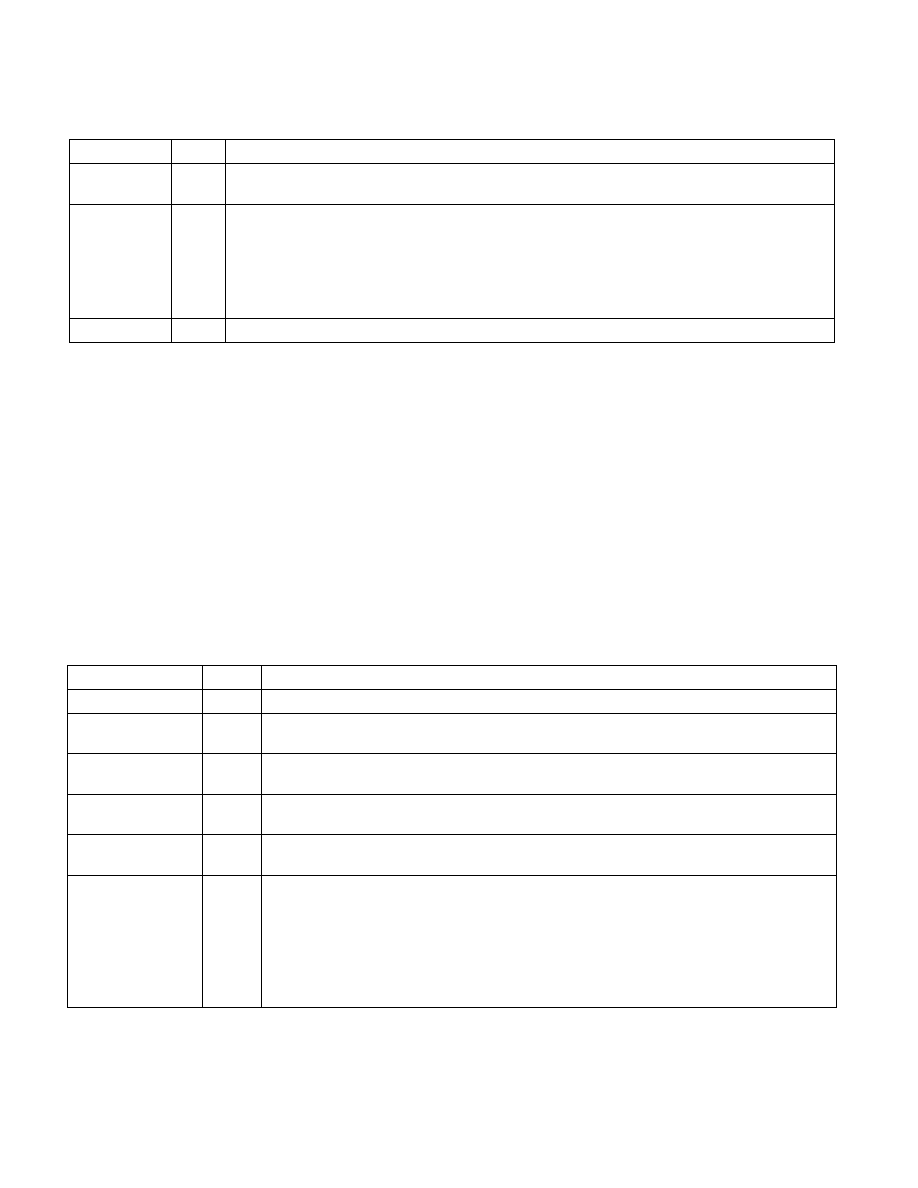

Table 18-57. Layout of Data Linear Address Information In PEBS Record

Field Offset

Description

Data Linear

Address

98H

The linear address of the load or the destination of the store.

Store Status

A0H

• DCU Hit (Bit 0): The store hit the data cache closest to the core (L1 cache) if this bit is set, otherwise

the store missed the data cache. This information is valid only for the following store events:

UOPS_RETIRED.ALL (if store is tagged),

MEM_INST_RETIRED.STLB_MISS_STORES,

MEM_INST_RETIRED.ALL_STORES,

MEM_INST_RETIRED.SPLIT_STORES.

• Other bits are zero.

Reserved

A8H

Always zero.

Table 18-58. FrontEnd_Retired Sub-Event Encodings Supported by MSR_PEBS_FRONTEND.EVTSEL

Sub-Event Name

EVTSEL Description

DSB_MISS

11H

Retired Instructions which experienced decode stream buffer (DSB) miss.

L1I_MISS

12H

The fetch of retired Instructions which experienced Instruction L1 Cache true miss

1

. Additional

requests to the same cache line as an in-flight L1I cache miss will not be counted.

NOTES:

1. A true miss is the first miss for a cacheline/page (excluding secondary misses that fall into same cacheline/page).

L2_MISS

13H

The fetch of retired Instructions which experienced L2 Cache true miss. Additional requests to the

same cache line as an in-flight MLC cache miss will not be counted.

ITLB_MISS

14H

The fetch of retired Instructions which experienced ITLB true miss. Additional requests to the same

cache line as an in-flight ITLB miss will not be counted.

STLB_MISS

15H

The fetch of retired Instructions which experienced STLB true miss. Additional requests to the

same cache line as an in-flight STLB miss will not be counted.

IDQ_READ_BUBBLES 6H

An IDQ read bubble is defined as any one of the 4 allocation slots of IDQ that is not filled by the

front-end on any cycle where there is no back end stall. Using the threshold and latency fields in

MSR_PEBS_FRONTEND allows counting of IDQ read bubbles of various magnitude and duration.

Latency controls the number of cycles and Threshold controls the number of allocation slots that

contain bubbles.

The event counts if and only if a sequence of at least FE_LATENCY consecutive cycles contain at

least FE_TRESHOLD number of bubbles each.