Vol. 3B 18-53

PERFORMANCE MONITORING

18.9.2 Counter

Coalescence

In processors based on Intel microarchitecture code name Sandy Bridge, each processor core implements eight

general-purpose counters. CPUID.0AH:EAX[15:8] will report either 4 or 8 depending specific processor’s product

features.

If a processor core is shared by two logical processors, each logical processors can access 4 counters (IA32_PMC0-

IA32_PMC3). This is the same as in the prior generation for processors based on Intel microarchitecture code name

Nehalem.

If a processor core is not shared by two logical processors, all eight general-purpose counters are visible, and

CPUID.0AH:EAX[15:8] reports 8. IA32_PMC4-IA32_PMC7 occupy MSR addresses 0C5H through 0C8H. Each

counter is accompanied by an event select MSR (IA32_PERFEVTSEL4-IA32_PERFEVTSEL7).

If CPUID.0AH:EAX[15:8] report 4, access to IA32_PMC4-IA32_PMC7, IA32_PMC4-IA32_PMC7 will cause #GP.

Writing 1’s to bit position 7:4 of IA32_PERF_GLOBAL_CTRL, IA32_PERF_GLOBAL_STATUS, or

IA32_PERF_GLOBAL_OVF_CTL will also cause #GP.

18.9.3

Full Width Writes to Performance Counters

Processors based on Intel microarchitecture code name Sandy Bridge support full-width writes to the general-

purpose counters, IA32_PMCx. Support of full-width writes are enumerated by

IA32_PERF_CAPABILITIES.FW_WRITES[13] (see Section 18.2.4).

The default behavior of IA32_PMCx is unchanged, i.e. WRMSR to IA32_PMCx results in a sign-extended 32-bit

value of the input EAX written into IA32_PMCx. Full-width writes must issue WRMSR to a dedicated alias MSR

address for each IA32_PMCx.

Software must check the presence of full-width write capability and the presence of the alias address

IA32_A_PMCx by testing IA32_PERF_CAPABILITIES[13].

18.9.4

PEBS Support in Intel

®

Microarchitecture Code Name Sandy Bridge

Processors based on Intel microarchitecture code name Sandy Bridge support PEBS, similar to those offered in

prior generation, with several enhanced features. The key components and differences of PEBS facility relative to

Intel microarchitecture code name Westmere is summarized in Table 18-31.

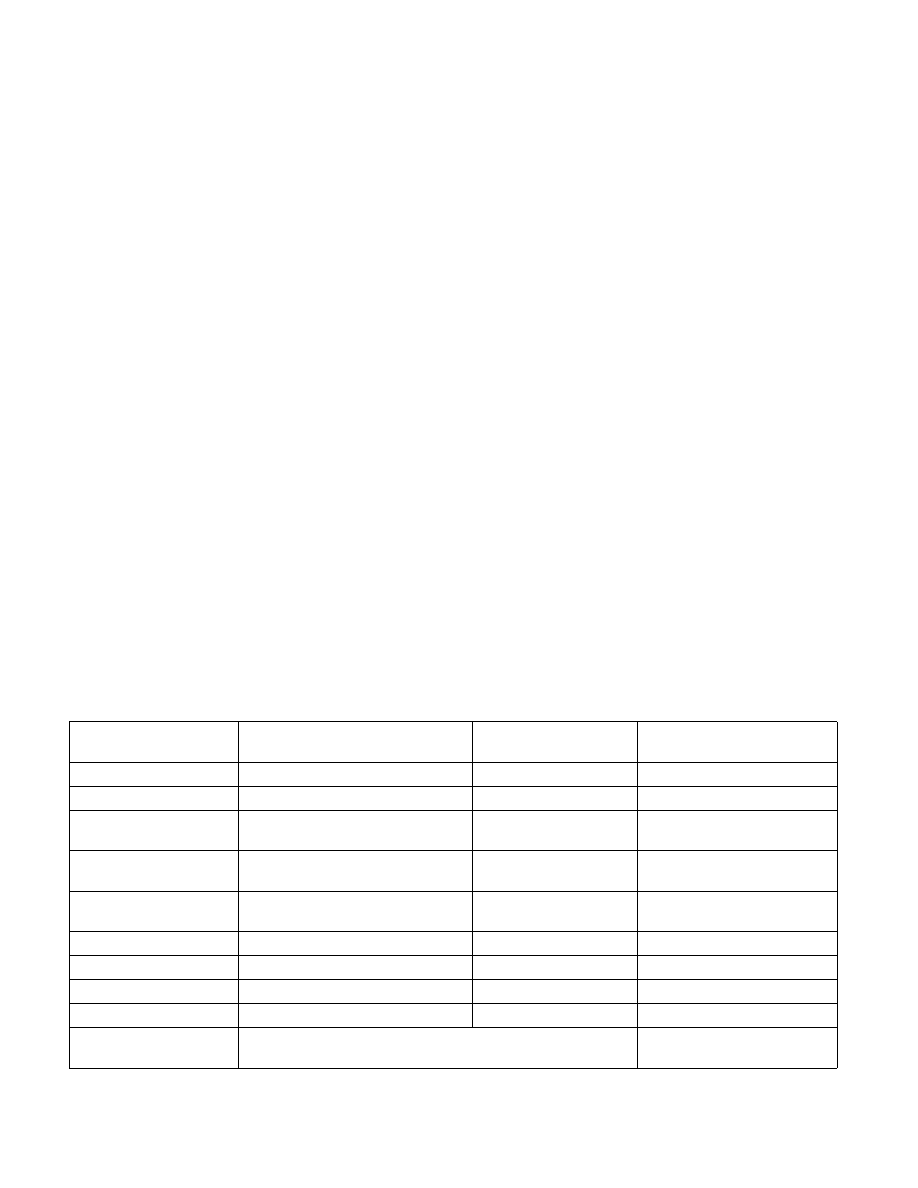

Table 18-31. PEBS Facility Comparison

Box

Intel® microarchitecture code name

Sandy Bridge

Intel® microarchitecture

code name Westmere

Comment

Valid IA32_PMCx

PMC0-PMC3

PMC0-PMC3

No PEBS on PMC4-PMC7.

PEBS Buffer Programming

Unchanged

IA32_PEBS_ENABLE

Layout

PEBS record layout

Physical Layout same as Table 18-23.

Enhanced fields at offsets 98H,

A0H, A8H.

PEBS Events

IA32_PMC4-IA32_PMC7 do not

support PEBS.

PEBS-Load Latency

See Table 18-33.

PEBS-Precise Store

Yes; see Section 18.9.4.3.

No

IA32_PMC3 only

PEBS-PDIR

Yes

No

IA32_PMC1 only

PEBS skid from EventingIP

1 (or 2 if micro+macro fusion)

1

SAMPLING Restriction

Small SAV(CountDown) value incur higher overhead than prior

generation.