18-36 Vol. 3B

PERFORMANCE MONITORING

When a counter is enabled to capture machine state (PEBS_EN_PMCx = 1), the processor will write machine state

information to a memory buffer specified by software as detailed below. When the counter IA32_PMCx overflows

from maximum count to zero, the PEBS hardware is armed.

Upon occurrence of the next PEBS event, the PEBS hardware triggers an assist and causes a PEBS record to be

written. The format of the PEBS record is indicated by the bit field IA32_PERF_CAPABILITIES[11:8] (see

Figure 18-49).

The behavior of PEBS assists is reported by IA32_PERF_CAPABILITIES[6] (see Figure 18-49). The return instruc-

tion pointer (RIP) reported in the PEBS record will point to the instruction after (+1) the instruction that causes the

PEBS assist. The machine state reported in the PEBS record is the machine state after the instruction that causes

the PEBS assist is retired. For instance, if the instructions:

mov eax, [eax] ; causes PEBS assist

nop

are executed, the PEBS record will report the address of the nop, and the value of EAX in the PEBS record will show

the value read from memory, not the target address of the read operation.

The PEBS record format is shown in Table 18-23, and each field in the PEBS record is 64 bits long. The PEBS record

format, along with debug/store area storage format, does not change regardless of IA-32e mode is active or not.

CPUID.01H:ECX.DTES64[bit 2] reports whether the processor's DS storage format support is mode-independent.

When set, it uses 64-bit DS storage format.

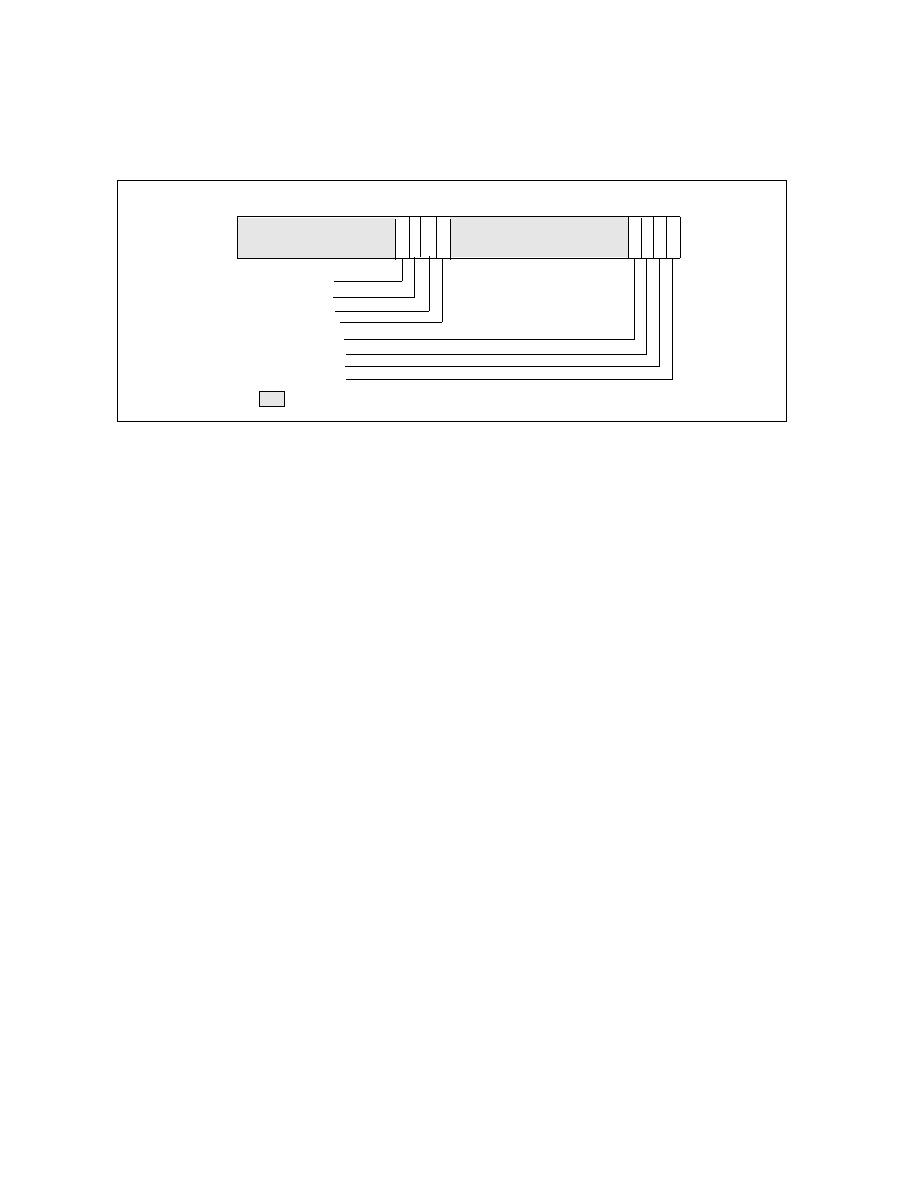

Figure 18-21. Layout of IA32_PEBS_ENABLE MSR

LL_EN_PMC3 (R/W)

LL_EN_PMC2 (R/W)

8 7

0

LL_EN_PMC1 (R/W)

32

3

33

1

Reserved

63

2

4

31

5

6

34

35

36

PEBS_EN_PMC3 (R/W)

PEBS_EN_PMC2 (R/W)

PEBS_EN_PMC1 (R/W)

PEBS_EN_PMC0 (R/W)

LL_EN_PMC0 (R/W)

RESET Value — 00000000_00000000H