Vol. 3B 18-37

PERFORMANCE MONITORING

In IA-32e mode, the full 64-bit value is written to the register. If the processor is not operating in IA-32e mode, 32-

bit value is written to registers with bits 63:32 zeroed. Registers not defined when the processor is not in IA-32e

mode are written to zero.

Bytes AFH:90H are enhancement to the PEBS record format. Support for this enhanced PEBS record format is indi-

cated by IA32_PERF_CAPABILITIES[11:8] encoding of 0001B.

The value written to bytes 97H:90H is the state of the IA32_PERF_GLOBAL_STATUS register before the PEBS assist

occurred. This value is written so software can determine which counters overflowed when this PEBS record was

written. Note that this field indicates the overflow status for all counters, regardless of whether they were

programmed for PEBS or not.

Programming PEBS Facility

Only a subset of non-architectural performance events in the processor support PEBS. The subset of precise events

are listed in Table 18-10. In addition to using IA32_PERFEVTSELx to specify event unit/mask settings and setting

the EN_PMCx bit in the IA32_PEBS_ENABLE register for the respective counter, the software must also initialize the

DS_BUFFER_MANAGEMENT_AREA data structure in memory to support capturing PEBS records for precise events.

NOTE

PEBS events are only valid when the following fields of IA32_PERFEVTSELx are all zero: AnyThread,

Edge, Invert, CMask.

The beginning linear address of the DS_BUFFER_MANAGEMENT_AREA data structure must be programmed into

the IA32_DS_AREA register. The layout of the DS_BUFFER_MANAGEMENT_AREA is shown in Figure 18-22.

•

PEBS Buffer Base: This field is programmed with the linear address of the first byte of the PEBS buffer

allocated by software. The processor reads this field to determine the base address of the PEBS buffer.

Software should allocate this memory from the non-paged pool.

•

PEBS Index: This field is initially programmed with the same value as the PEBS Buffer Base field, or the

beginning linear address of the PEBS buffer. The processor reads this field to determine the location of the next

PEBS record to write to. After a PEBS record has been written, the processor also updates this field with the

address of the next PEBS record to be written. The figure above illustrates the state of PEBS Index after the

first PEBS record is written.

•

PEBS Absolute Maximum: This field represents the absolute address of the maximum length of the allocated

PEBS buffer plus the starting address of the PEBS buffer. The processor will not write any PEBS record beyond

the end of PEBS buffer, when PEBS Index equals PEBS Absolute Maximum. No signaling is generated when

PEBS buffer is full. Software must reset the PEBS Index field to the beginning of the PEBS buffer address to

continue capturing PEBS records.

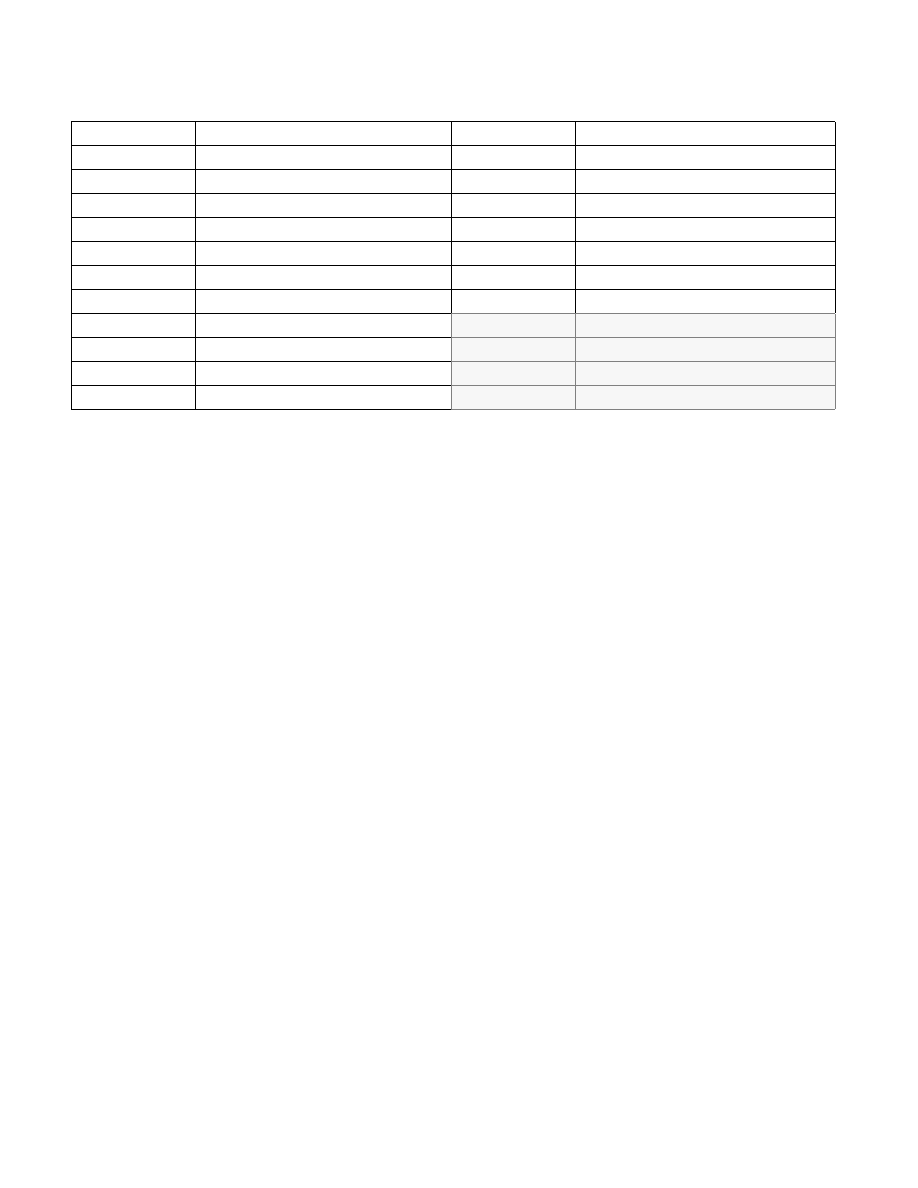

Table 18-23. PEBS Record Format for Intel Core i7 Processor Family

Byte Offset

Field

Byte Offset

Field

00H

R/EFLAGS

58H

R9

08H

R/EIP

60H

R10

10H

R/EAX

68H

R11

18H

R/EBX

70H

R12

20H

R/ECX

78H

R13

28H

R/EDX

80H

R14

30H

R/ESI

88H

R15

38H

R/EDI

90H

IA32_PERF_GLOBAL_STATUS

40H

R/EBP

98H

Data Linear Address

48H

R/ESP

A0H

Data Source Encoding

50H

R8

A8H

Latency value (core cycles)