Vol. 3C 35-241

MODEL-SPECIFIC REGISTERS (MSRS)

35.15 MSRS IN THE 6TH GENERATION INTEL

®

CORE

™

PROCESSORS

The 6th generation Intel

®

Core™ processor family is based on the Skylake microarchitecture. They have CPUID

DisplayFamily_DisplayModel signatures of 06_4EH and 06_5EH, supports the MSR interfaces listed in Table 35-18,

Table 35-19, Table 35-23, Table 35-27, Table 35-33, Table 35-37, and Table 35-38. For an MSR listed in Table 35-37

that also appears in the model-specific tables of prior generations, Table 35-37 supercede prior generation tables.

The notation of “Platform” in the Scope column (with respect to MSR_PLATFORM_ENERGY_COUNTER and

MSR_PLATFORM_POWER_LIMIT) is limited to the power-delivery domain and the specifics of the power delivery

integration may vary by platform vendor’s implementation.

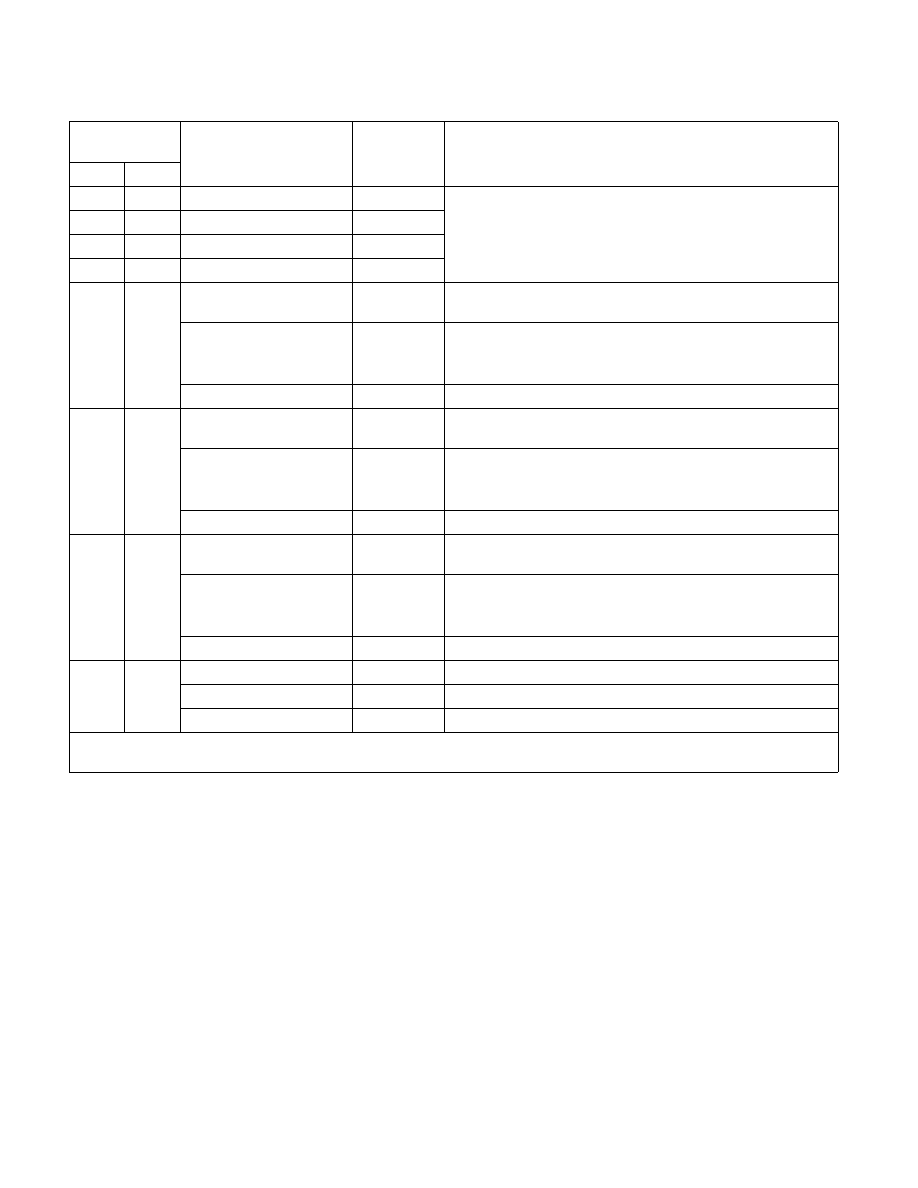

454H

1108

IA32_MC21_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC21 reports MC error from the Intel QPI 2 module.

455H

1109

IA32_MC21_STATUS

Package

456H

1110

IA32_MC21_ADDR

Package

457H

1111

IA32_MC21_MISC

Package

630H

1584

MSR_PKG_C8_RESIDENCY

Package

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-States.

59:0

Package C8 Residency Counter. (R/O)

Value since last reset that this package is in processor-specific C8

states. Count at the same frequency as the TSC.

63:60

Reserved

631H

1585

MSR_PKG_C9_RESIDENCY

Package

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-States.

59:0

Package C9 Residency Counter. (R/O)

Value since last reset that this package is in processor-specific C9

states. Count at the same frequency as the TSC.

63:60

Reserved

632H

1586

MSR_PKG_C10_RESIDENCY Package

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-States.

59:0

Package C10 Residency Counter. (R/O)

Value since last reset that this package is in processor-specific C10

states. Count at the same frequency as the TSC.

63:60

Reserved

C81H

3201

IA32_L3_QOS_CFG

Package

Cache Allocation Technology Configuration (R/W)

0

CAT Enable. Set 1 to enable Cache Allocation Technology

63:1

Reserved.

See Table 35-18, Table 35-19, Table 35-27, and Table 35-28 for other MSR definitions applicable to processors with CPUID signature

06_45H.

NOTES:

1. An override configuration lower than the factory-set configuration is always supported. An override configuration higher than the fac-

tory-set configuration is dependent on features specific to the processor and the platform.

Table 35-36. Additional MSRs Supported by Intel® Xeon® Processors with DisplayFamily_DisplayModel 06_4FH

Register

Address

Register Name

Scope

Bit Description

Hex

Dec