35-242 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

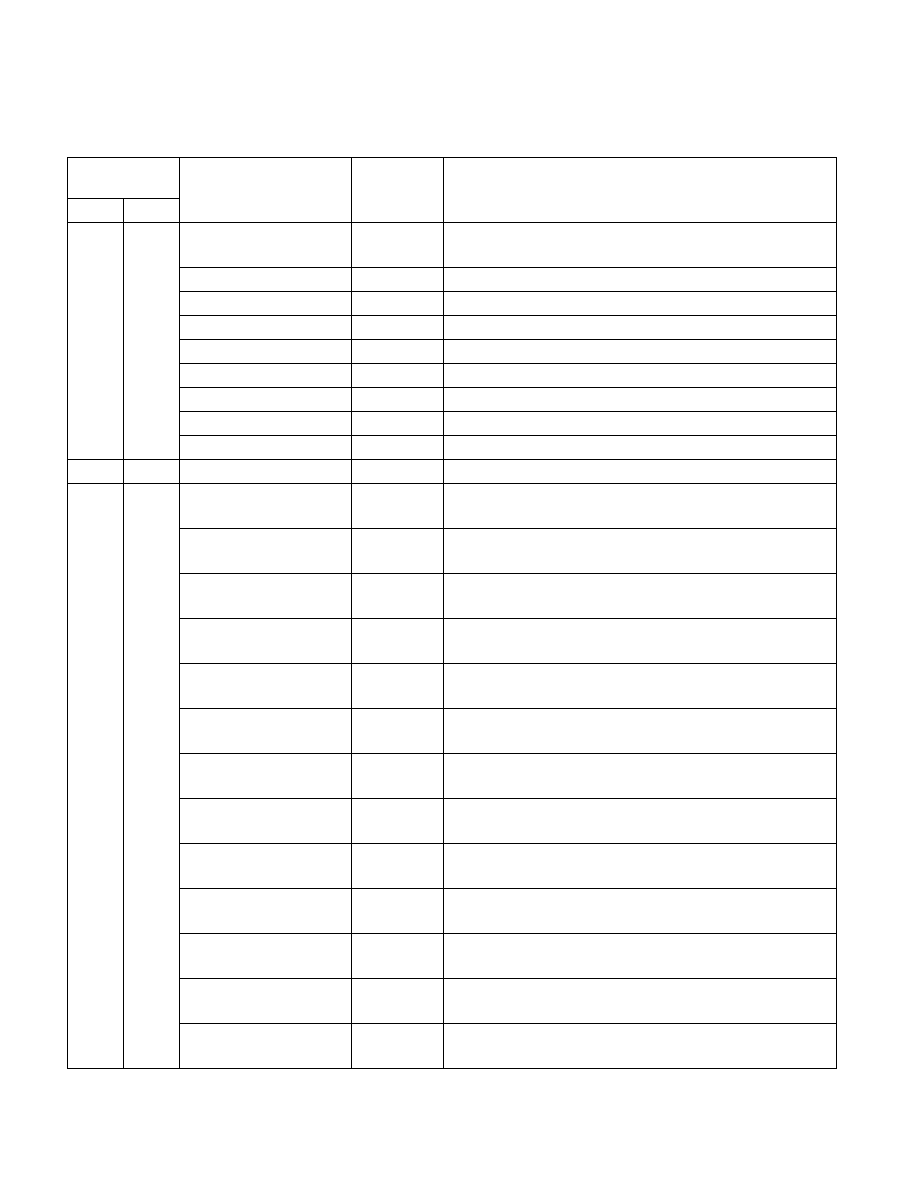

Table 35-37. Additional MSRs Supported by 6th Generation Intel® Core™ Processors Based on Skylake

Microarchitecture

Register

Address

Register Name

Scope

Bit Description

Hex

Dec

3AH

58

IA32_FEATURE_CONTROL

Thread

Control Features in Intel 64 Processor (R/W)

See Table 35-2.

0

Lock (R/WL)

1

Enable VMX inside SMX operation (R/WL)

2

Enable VMX outside SMX operation (R/WL)

14:8

SENTER local functions enables (R/WL)

15

SENTER global functions enable (R/WL)

18

SGX global functions enable (R/WL)

20

LMCE_ON (R/WL)

63:21

Reserved.

FEH

254

IA32_MTRRCAP

Thread

MTRR Capality (RO, Architectural). See Table 35-2

19CH

412

IA32_THERM_STATUS

Core

Thermal Monitor Status (R/W)

See Table 35-2.

0

Thermal status (RO)

See Table 35-2.

1

Thermal status log (R/WC0)

See Table 35-2.

2

PROTCHOT # or FORCEPR# status (RO)

See Table 35-2.

3

PROTCHOT # or FORCEPR# log (R/WC0)

See Table 35-2.

4

Critical Temperature status (RO)

See Table 35-2.

5

Critical Temperature status log (R/WC0)

See Table 35-2.

6

Thermal threshold #1 status (RO)

See Table 35-2.

7

Thermal threshold #1 log (R/WC0)

See Table 35-2.

8

Thermal threshold #2 status (RO)

See Table 35-2.

9

Thermal threshold #2 log (R/WC0)

See Table 35-2.

10

Power Limitation status (RO)

See Table 35-2.

11

Power Limitation log (R/WC0)

See Table 35-2.