Vol. 3C 35-193

MODEL-SPECIFIC REGISTERS (MSRS)

35.11.1 MSRs in 4th Generation Intel

®

Core™ Processor Family (based on Haswell

Microarchitecture)

Table 35-28 lists model-specific registers (MSRs) that are specific to 4th generation Intel

®

Core™ processor family

and Intel

®

Xeon

®

processor E3-1200 v3 product family (based on Haswell microarchitecture). These processors

have a CPUID signature with DisplayFamily_DisplayModel of 06_3CH/06_45H/06_46H, see Table 35-1.

31

Config_TDP_Lock (RW/L)

When this bit is set, the content of this register is locked until a

reset.

63:32

Reserved.

64CH

1612

MSR_TURBO_ACTIVATION_

RATIO

Package

ConfigTDP Control (R/W)

7:0

MAX_NON_TURBO_RATIO (RW/L)

System BIOS can program this field.

30:8

Reserved.

31

TURBO_ACTIVATION_RATIO_Lock (RW/L)

When this bit is set, the content of this register is locked until a

reset.

63:32

Reserved.

C80H

3200

IA32_DEBUG_INTERFACE

Package

Silicon Debug Feature Control (R/W)

See Table 35-2.

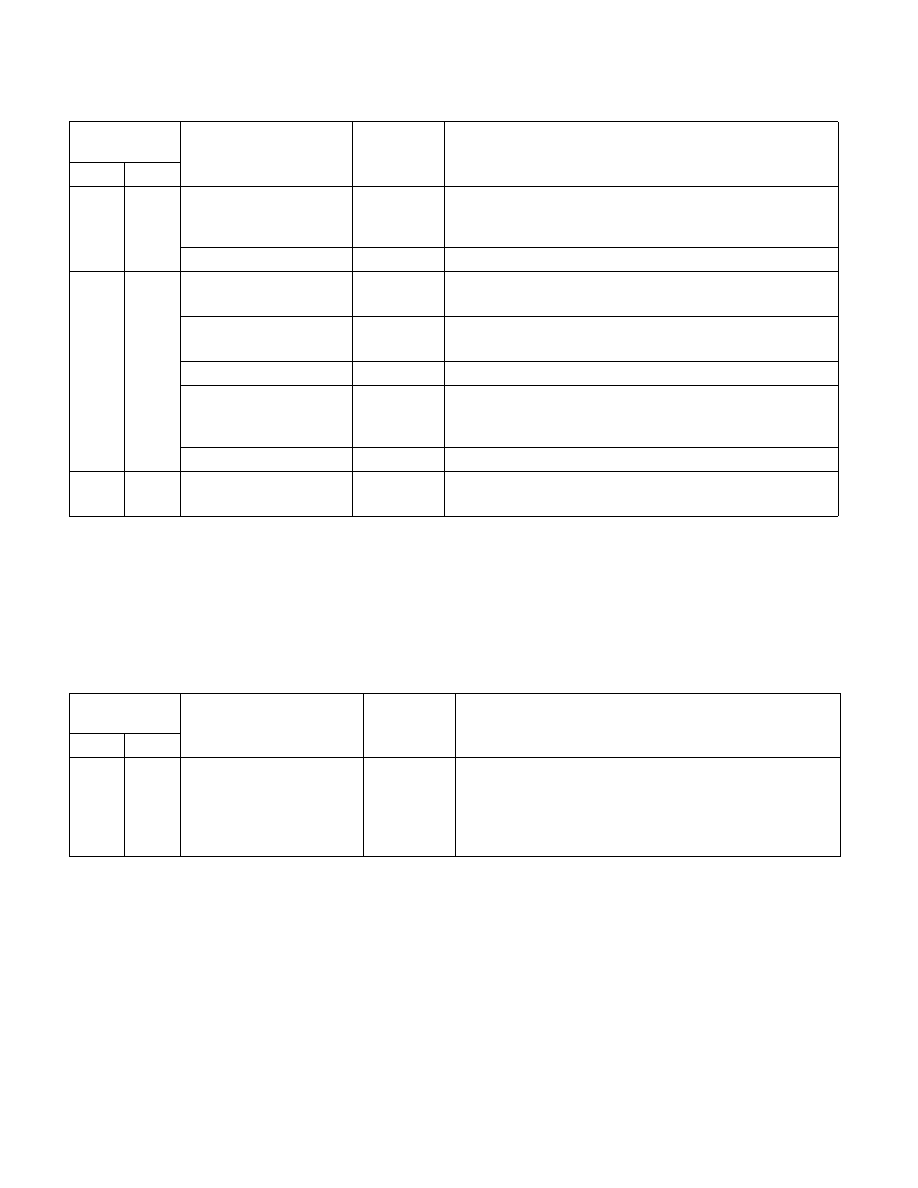

Table 35-28. MSRs Supported by 4th Generation Intel® Core™ Processors (Haswell microarchitecture)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec

E2H

226

MSR_PKG_CST_CONFIG_

CONTROL

Core

C-State Configuration Control (R/W)

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-

states.

See http://biosbits.org.

Table 35-27. Additional MSRs Supported by Processors based on the Haswell or Haswell-E microarchitectures

Register

Address

Register Name

Scope

Bit Description

Hex

Dec