35-172 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

35.10 MSRS IN THE 3RD GENERATION INTEL

®

CORE

™

PROCESSOR FAMILY

(BASED ON INTEL

®

MICROARCHITECTURE CODE NAME IVY BRIDGE)

The 3rd generation Intel

®

Core™ processor family and the Intel

®

Xeon

®

processor E3-1200v2 product family

(based on Intel microarchitecture code name Ivy Bridge) support the MSR interfaces listed in Table 35-18, Table

35-19, Table 35-20, and Table 35-23. These processors have a CPUID signature with DisplayFamily_DisplayModel

of 06_3AH.

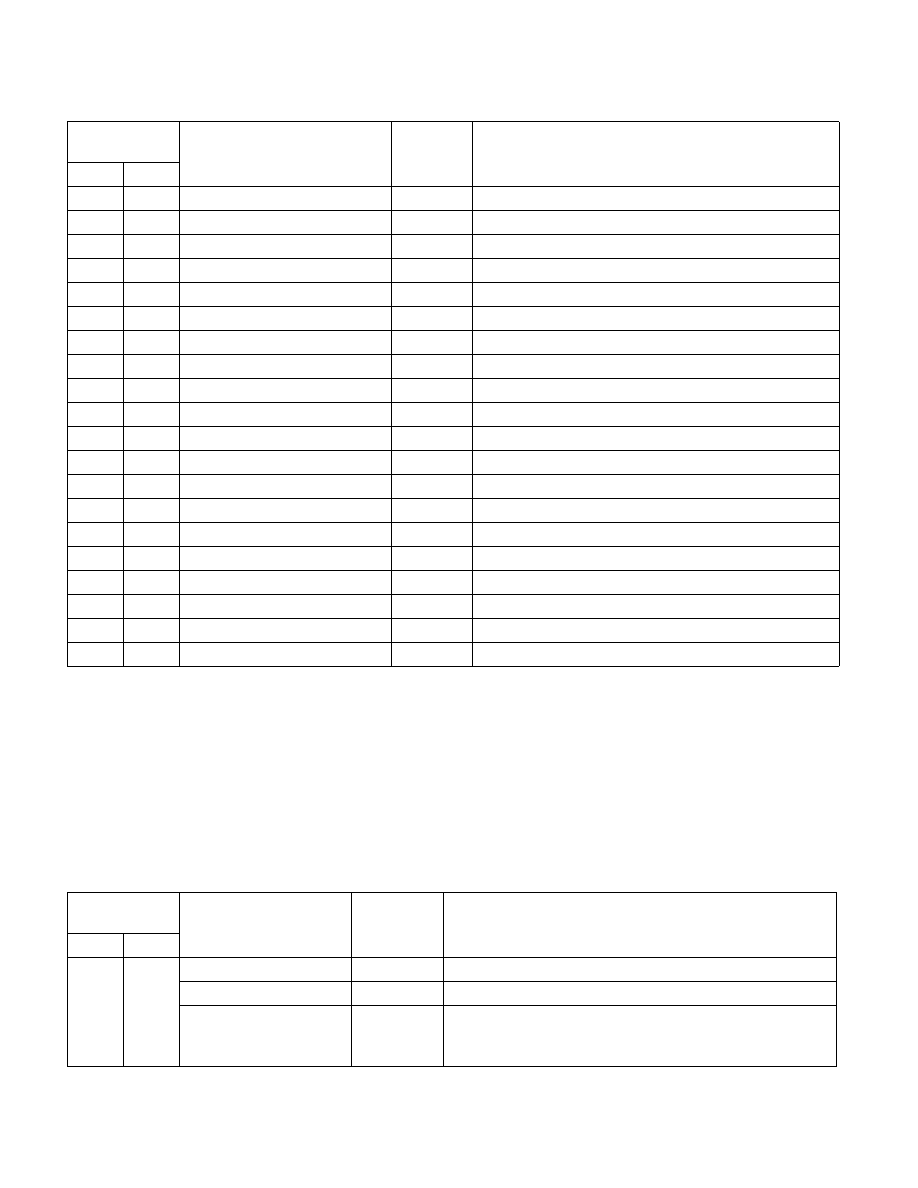

DC4H

MSR_C6_PMON_BOX_CTL

Package

Uncore C-box 6 perfmon local box wide control.

DD0H

MSR_C6_PMON_EVNTSEL0

Package

Uncore C-box 6 perfmon event select for C-box 6 counter 0.

DD1H

MSR_C6_PMON_EVNTSEL1

Package

Uncore C-box 6 perfmon event select for C-box 6 counter 1.

DD2H

MSR_C6_PMON_EVNTSEL2

Package

Uncore C-box 6 perfmon event select for C-box 6 counter 2.

DD3H

MSR_C6_PMON_EVNTSEL3

Package

Uncore C-box 6 perfmon event select for C-box 6 counter 3.

DD4H

MSR_C6_PMON_BOX_FILTER

Package

Uncore C-box 6 perfmon box wide filter.

DD6H

MSR_C6_PMON_CTR0

Package

Uncore C-box 6 perfmon counter 0.

DD7H

MSR_C6_PMON_CTR1

Package

Uncore C-box 6 perfmon counter 1.

DD8H

MSR_C6_PMON_CTR2

Package

Uncore C-box 6 perfmon counter 2.

DD9H

MSR_C6_PMON_CTR3

Package

Uncore C-box 6 perfmon counter 3.

DE4H

MSR_C7_PMON_BOX_CTL

Package

Uncore C-box 7 perfmon local box wide control.

DF0H

MSR_C7_PMON_EVNTSEL0

Package

Uncore C-box 7 perfmon event select for C-box 7 counter 0.

DF1H

MSR_C7_PMON_EVNTSEL1

Package

Uncore C-box 7 perfmon event select for C-box 7 counter 1.

DF2H

MSR_C7_PMON_EVNTSEL2

Package

Uncore C-box 7 perfmon event select for C-box 7 counter 2.

DF3H

MSR_C7_PMON_EVNTSEL3

Package

Uncore C-box 7 perfmon event select for C-box 7 counter 3.

DF4H

MSR_C7_PMON_BOX_FILTER

Package

Uncore C-box 7 perfmon box wide filter.

DF6H

MSR_C7_PMON_CTR0

Package

Uncore C-box 7 perfmon counter 0.

DF7H

MSR_C7_PMON_CTR1

Package

Uncore C-box 7 perfmon counter 1.

DF8H

MSR_C7_PMON_CTR2

Package

Uncore C-box 7 perfmon counter 2.

DF9H

MSR_C7_PMON_CTR3

Package

Uncore C-box 7 perfmon counter 3.

Table 35-23. Additional MSRs Supported by 3rd Generation Intel® Core™ Processors (based on Intel®

microarchitecture code name Ivy Bridge)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec

CEH

206

MSR_PLATFORM_INFO

Package

See http://biosbits.org.

7:0

Reserved.

15:8

Package

Maximum Non-Turbo Ratio (R/O)

The is the ratio of the frequency that invariant TSC runs at.

Frequency = ratio * 100 MHz.

Table 35-22. Uncore PMU MSRs in Intel® Xeon® Processor E5 Family (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec