Vol. 3B 15-9

MACHINE-CHECK ARCHITECTURE

occurred. Software may re-read IA32_MCi_STATUS, IA32_MCi_ADDR and IA32_MCi_MISC appropriately to ensure

data collected represent the last error logged.

After software polls a posting and clears the register, the valid bit is no longer set and therefore the meaning of the

rest of the bits, including the yellow/green/00 status field in bits 54:53, is undefined. The yellow/green indication

will only be posted for events associated with monitored structures – otherwise the unmonitored (00) code will be

posted in IA32_MC

i

_STATUS[54:53].

15.3.2.3 IA32_MCi_ADDR MSRs

The IA32_MCi_ADDR MSR contains the address of the code or data memory location that produced the machine-

check error if the ADDRV flag in the IA32_MCi_STATUS register is set (see Section 15-7, “IA32_MCi_ADDR MSR”).

The IA32_MCi_ADDR register is either not implemented or contains no address if the ADDRV flag in the

IA32_MCi_STATUS register is clear. When not implemented in the processor, all reads and writes to this MSR will

cause a general protection exception.

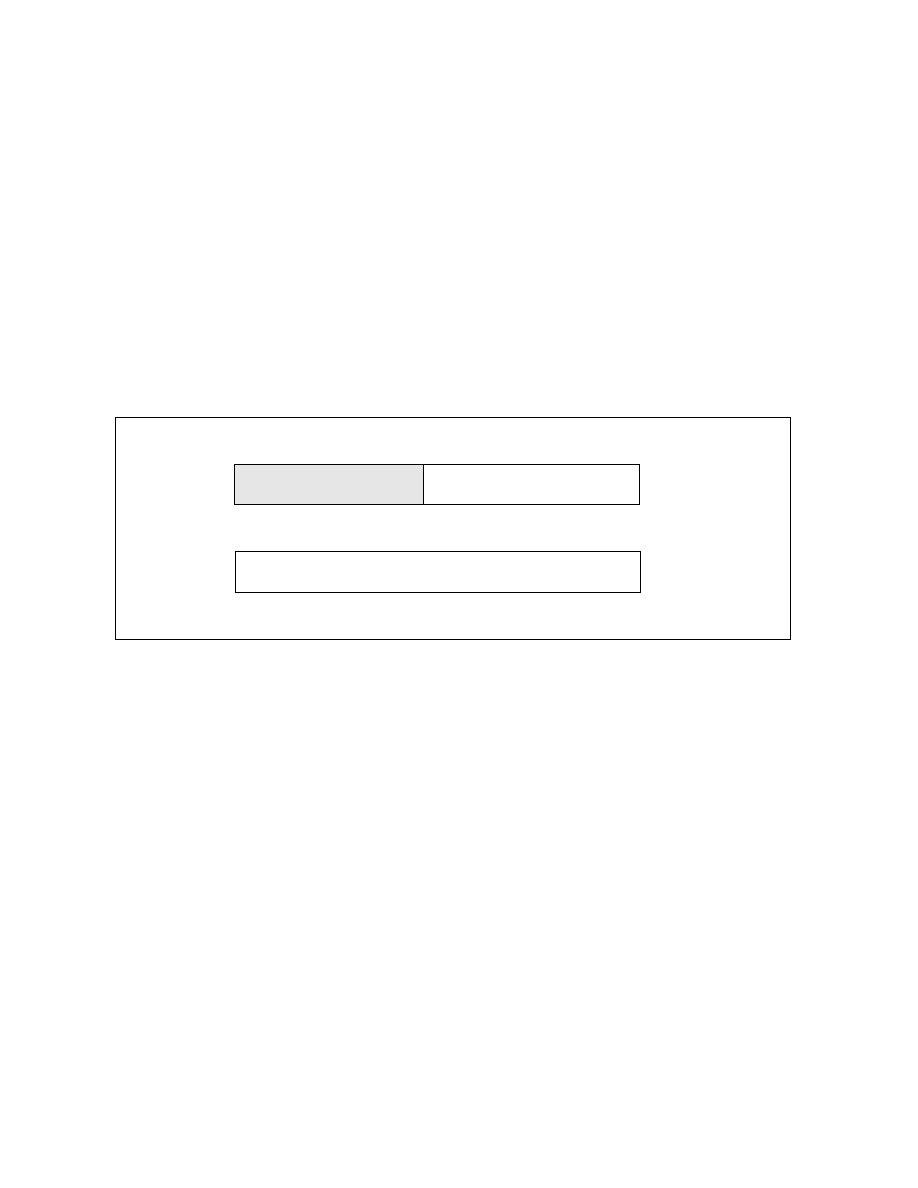

The address returned is an offset into a segment, linear address, or physical address. This depends on the error

encountered. When these registers are implemented, these registers can be cleared by explicitly writing 0s to

these registers. Writing 1s to these registers will cause a general-protection exception. See Figure 15-7.

15.3.2.4 IA32_MC

i

_MISC MSRs

The IA32_MCi_MISC MSR contains additional information describing the machine-check error if the MISCV flag in

the IA32_MCi_STATUS register is set. The IA32_MCi_MISC_MSR is either not implemented or does not contain

additional information if the MISCV flag in the IA32_MCi_STATUS register is clear.

When not implemented in the processor, all reads and writes to this MSR will cause a general protection exception.

When implemented in a processor, these registers can be cleared by explicitly writing all 0s to them; writing 1s to

them causes a general-protection exception to be generated. This register is not implemented in any of the error-

reporting register banks for the P6 or Intel Atom family processors.

If both MISCV and IA32_MCG_CAP[24] are set, the IA32_MCi_MISC_MSR is defined according to Figure 15-8 to

support software recovery of uncorrected errors (see Section 15.6):

Figure 15-7. IA32_MCi_ADDR MSR

Address

63

0

Reserved

35

36

Address

*

63

0

Processor Without Support For Intel 64 Architecture

Processor With Support for Intel 64 Architecture

*

Useful bits in this field depend on the address methodology in use when the

the register state is saved.