35-188 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

35.11 MSRS IN THE 4TH GENERATION INTEL

®

CORE

™

PROCESSORS (BASED ON

HASWELL MICROARCHITECTURE)

The 4th generation Intel

®

Core™ processor family and Intel

®

Xeon

®

processor E3-1200v3 product family (based

on Haswell microarchitecture), with CPUID DisplayFamily_DisplayModel signature 06_3CH/06_45H/06_46H,

support the MSR interfaces listed in Table 35-18, Table 35-19, Table 35-20, and Table 35-27. For an MSR listed in

Table 35-18 that also appears in Table 35-27, Table 35-27 supercede Table 35-18.

The MSRs listed in Table 35-27 also apply to processors based on Haswell-E microarchitecture (see Section 35.12).

EB0H

MSR_C13_PMON_EVNTSEL0

Package

Uncore C-box 13 perfmon event select for C-box 13 counter 0.

EB1H

MSR_C13_PMON_EVNTSEL1

Package

Uncore C-box 13 perfmon event select for C-box 13 counter 1.

EB2H

MSR_C13_PMON_EVNTSEL2

Package

Uncore C-box 13 perfmon event select for C-box 13 counter 2.

EB3H

MSR_C13_PMON_EVNTSEL3

Package

Uncore C-box 13 perfmon event select for C-box 13 counter 3.

EB4H

MSR_C13_PMON_BOX_FILTER

Package

Uncore C-box 13 perfmon box wide filter.

EB6H

MSR_C13_PMON_CTR0

Package

Uncore C-box 13 perfmon counter 0.

EB7H

MSR_C13_PMON_CTR1

Package

Uncore C-box 13 perfmon counter 1.

EB8H

MSR_C13_PMON_CTR2

Package

Uncore C-box 13 perfmon counter 2.

EB9H

MSR_C13_PMON_CTR3

Package

Uncore C-box 13 perfmon counter 3.

EBAH

MSR_C13_PMON_BOX_FILTER1

Package

Uncore C-box 13 perfmon box wide filter1.

EC4H

MSR_C14_PMON_BOX_CTL

Package

Uncore C-box 14 perfmon local box wide control.

ED0H

MSR_C14_PMON_EVNTSEL0

Package

Uncore C-box 14 perfmon event select for C-box 14 counter 0.

ED1H

MSR_C14_PMON_EVNTSEL1

Package

Uncore C-box 14 perfmon event select for C-box 14 counter 1.

ED2H

MSR_C14_PMON_EVNTSEL2

Package

Uncore C-box 14 perfmon event select for C-box 14 counter 2.

ED3H

MSR_C14_PMON_EVNTSEL3

Package

Uncore C-box 14 perfmon event select for C-box 14 counter 3.

ED4H

MSR_C14_PMON_BOX_FILTER

Package

Uncore C-box 14 perfmon box wide filter.

ED6H

MSR_C14_PMON_CTR0

Package

Uncore C-box 14 perfmon counter 0.

ED7H

MSR_C14_PMON_CTR1

Package

Uncore C-box 14 perfmon counter 1.

ED8H

MSR_C14_PMON_CTR2

Package

Uncore C-box 14 perfmon counter 2.

ED9H

MSR_C14_PMON_CTR3

Package

Uncore C-box 14 perfmon counter 3.

EDAH

MSR_C14_PMON_BOX_FILTER1

Package

Uncore C-box 14 perfmon box wide filter1.

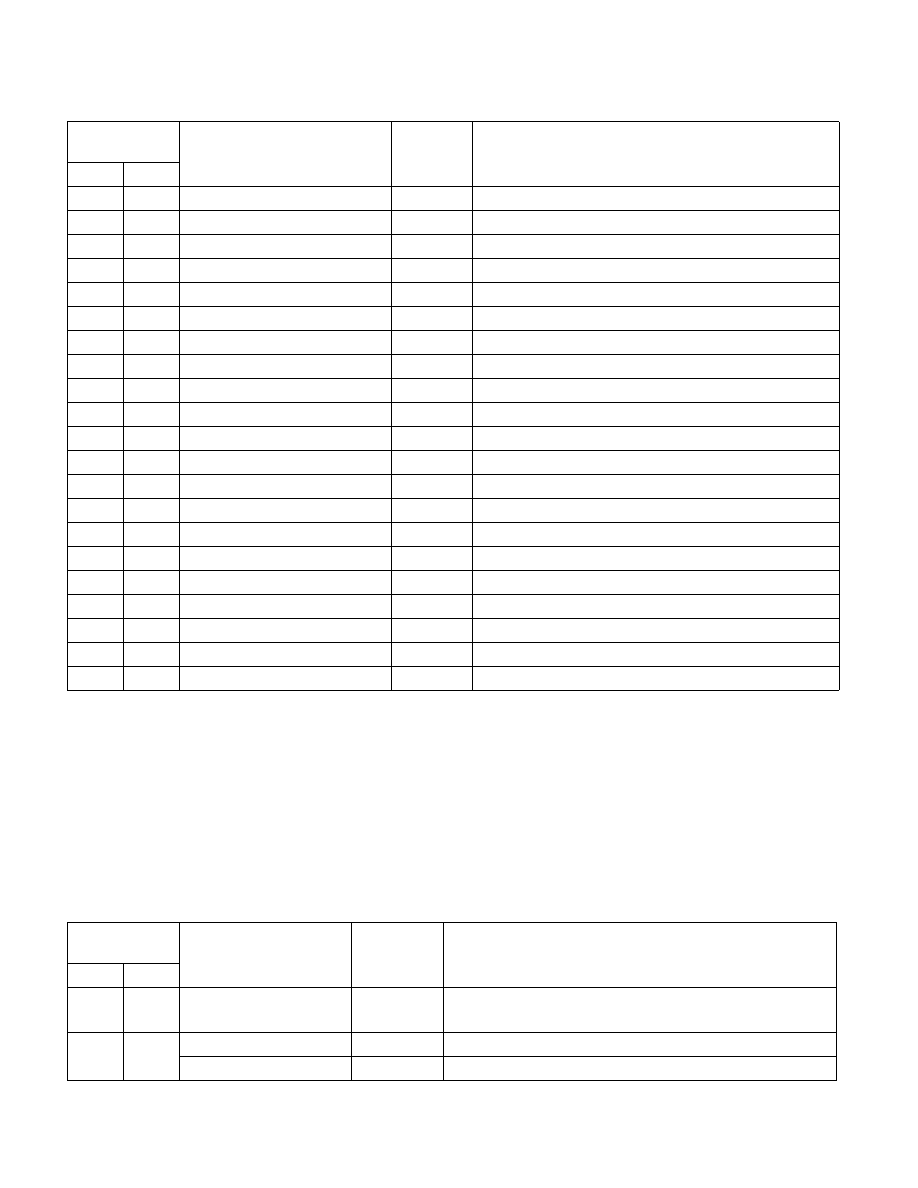

Table 35-27. Additional MSRs Supported by Processors based on the Haswell or Haswell-E microarchitectures

Register

Address

Register Name

Scope

Bit Description

Hex

Dec

3BH

59

IA32_TSC_ADJUST

THREAD

Per-Logical-Processor TSC ADJUST (R/W)

See Table 35-2.

CEH

206

MSR_PLATFORM_INFO

Package

7:0

Reserved.

Table 35-26. Uncore PMU MSRs in Intel® Xeon® Processor E5 v2 and E7 v2 Families (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec