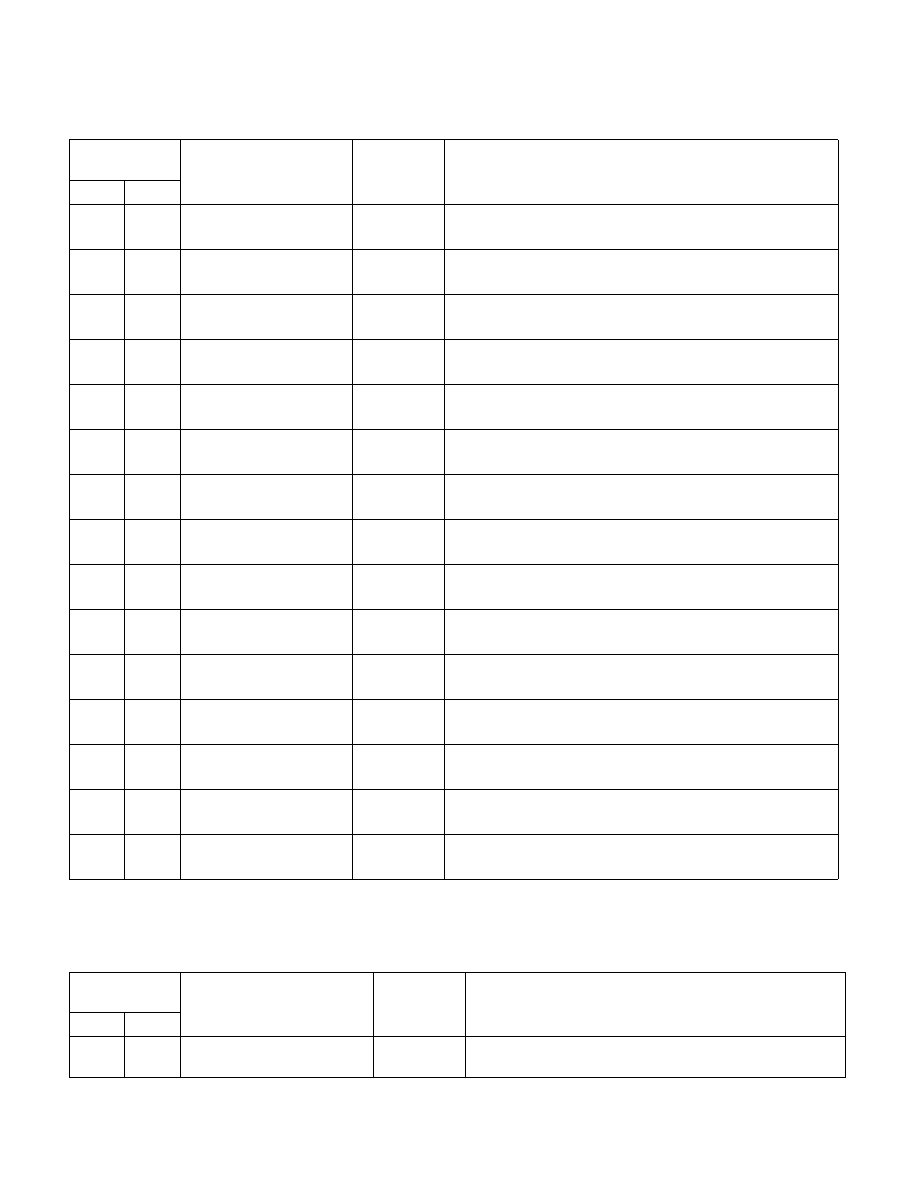

Vol. 3C 35-259

MODEL-SPECIFIC REGISTERS (MSRS)

Table 35-38 lists the MSRs of uncore PMU for Intel processors with CPUID DisplayFamily_DisplayModel signatures of

06_4EH and 06_5EH.

DD1H

3537

MSR_LBR_INFO_17

Thread

Last Branch Record 17 Additional Information (R/W)

See description of MSR_LBR_INFO_0.

DD2H

3538

MSR_LBR_INFO_18

Thread

Last Branch Record 18 Additional Information (R/W)

See description of MSR_LBR_INFO_0.

DD3H

3539

MSR_LBR_INFO_19

Thread

Last Branch Record 19 Additional Information (R/W)

See description of MSR_LBR_INFO_0.

DD4H

3520

MSR_LBR_INFO_20

Thread

Last Branch Record 20 Additional Information (R/W)

See description of MSR_LBR_INFO_0.

DD5H

3521

MSR_LBR_INFO_21

Thread

Last Branch Record 21 Additional Information (R/W)

See description of MSR_LBR_INFO_0.

DD6H

3522

MSR_LBR_INFO_22

Thread

Last Branch Record 22 Additional Information (R/W)

See description of MSR_LBR_INFO_0.

DD7H

3523

MSR_LBR_INFO_23

Thread

Last Branch Record 23 Additional Information (R/W)

See description of MSR_LBR_INFO_0.

DD8H

3524

MSR_LBR_INFO_24

Thread

Last Branch Record 24 Additional Information (R/W)

See description of MSR_LBR_INFO_0.

DD9H

3525

MSR_LBR_INFO_25

Thread

Last Branch Record 25 Additional Information (R/W)

See description of MSR_LBR_INFO_0.

DDAH

3526

MSR_LBR_INFO_26

Thread

Last Branch Record 26 Additional Information (R/W)

See description of MSR_LBR_INFO_0.

DDBH

3527

MSR_LBR_INFO_27

Thread

Last Branch Record 27 Additional Information (R/W)

See description of MSR_LBR_INFO_0.

DDCH

3528

MSR_LBR_INFO_28

Thread

Last Branch Record 28 Additional Information (R/W)

See description of MSR_LBR_INFO_0.

DDDH

3529

MSR_LBR_INFO_29

Thread

Last Branch Record 29 Additional Information (R/W)

See description of MSR_LBR_INFO_0.

DDEH

3530

MSR_LBR_INFO_30

Thread

Last Branch Record 30 Additional Information (R/W)

See description of MSR_LBR_INFO_0.

DDFH

3531

MSR_LBR_INFO_31

Thread

Last Branch Record 31 Additional Information (R/W)

See description of MSR_LBR_INFO_0.

Table 35-38. Uncore PMU MSRs Supported by 6th Generation Intel® Core™ Processors

Register

Address

Register Name

Scope

Bit Description

Hex

Dec

394H

916

MSR_UNC_PERF_FIXED_

CTRL

Package

Uncore fixed counter control (R/W)

Table 35-37. Additional MSRs Supported by 6th Generation Intel® Core™ Processors Based on Skylake

Microarchitecture

Register

Address

Register Name

Scope

Bit Description

Hex

Dec