35-238 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

35.14.2 Additional MSRs Supported in Intel® Xeon®

Processors E5 v4 and E7 v4 Families

The MSRs listed in Table 35-35 are available to Intel

®

Xeon

®

Processor E5 v4 and E7 v4 Families (CPUID

DisplayFamily_DisplayModel = 06_4FH). The Intel

®

Xeon

®

processor E5 v4 family is based on the Broadwell micro-

architecture and supports the MSR interfaces listed in Table 35-18, Table 35-19, Table 35-27, Table 35-32, Table

35-34, and Table 35-36.

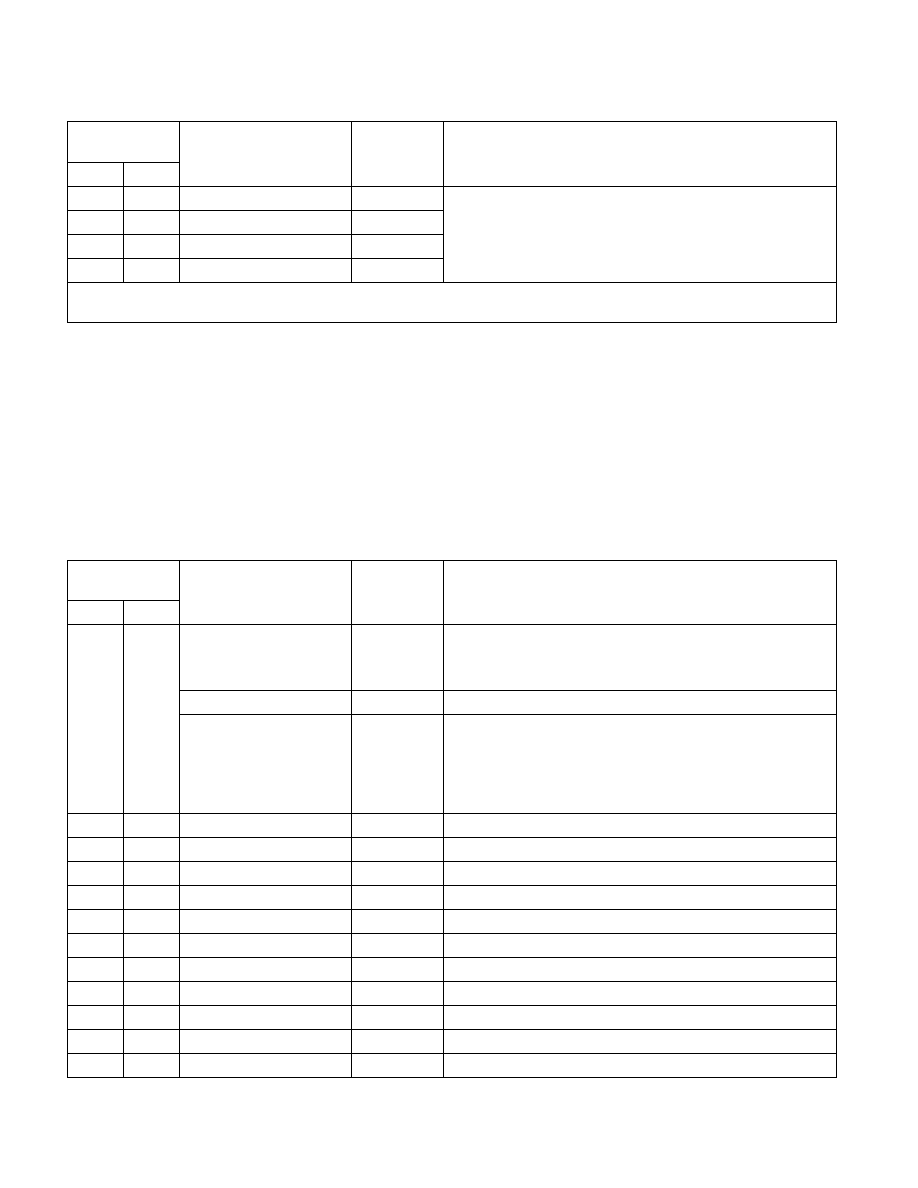

44CH

1100

IA32_MC19_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC19 reports MC error from the following pair of CBo/L3

Slices (if the pair is present): CBo2, CBo5, CBo8, CBo11, CBo14,

CBo17.

44DH

1101

IA32_MC19_STATUS

Package

44EH

1102

IA32_MC19_ADDR

Package

44FH

1103

IA32_MC19_MISC

Package

See Table 35-18, Table 35-27, Table 35-32, and Table 35-34 for other MSR definitions applicable to processors with CPUID signature

06_56H.

NOTES:

1. An override configuration lower than the factory-set configuration is always supported. An override configuration higher than the fac-

tory-set configuration is dependent on features specific to the processor and the platform.

Table 35-36. Additional MSRs Supported by Intel® Xeon® Processors with DisplayFamily_DisplayModel 06_4FH

Register

Address

Register Name

Scope

Bit Description

Hex

Dec

1ACH

428

MSR_TURBO_RATIO_LIMIT3 Package

Config Ratio Limit of Turbo Mode

RO if MSR_PLATFORM_INFO.[28] = 0,

RW if MSR_PLATFORM_INFO.[28] = 1

62:0

Package

Reserved

63

Package

Semaphore for Turbo Ratio Limit Configuration

If 1, the processor uses override configuration

1

specified in

MSR_TURBO_RATIO_LIMIT, MSR_TURBO_RATIO_LIMIT1 and

MSR_TURBO_RATIO_LIMIT2.

If 0, the processor uses factory-set configuration (Default).

285H

645

IA32_MC5_CTL2

Package

See Table 35-2.

286H

646

IA32_MC6_CTL2

Package

See Table 35-2.

287H

647

IA32_MC7_CTL2

Package

See Table 35-2.

288H

648

IA32_MC8_CTL2

Package

See Table 35-2.

289H

649

IA32_MC9_CTL2

Package

See Table 35-2.

28AH

650

IA32_MC10_CTL2

Package

See Table 35-2.

28BH

651

IA32_MC11_CTL2

Package

See Table 35-2.

28CH

652

IA32_MC12_CTL2

Package

See Table 35-2.

28DH

653

IA32_MC13_CTL2

Package

See Table 35-2.

28EH

654

IA32_MC14_CTL2

Package

See Table 35-2.

28FH

655

IA32_MC15_CTL2

Package

See Table 35-2.

Table 35-35. Additional MSRs Supported by Intel® Xeon® Processor D with DisplayFamily_DisplayModel 06_56H

Register

Address

Register Name

Scope

Bit Description

Hex

Dec