Vol. 3C 35-227

MODEL-SPECIFIC REGISTERS (MSRS)

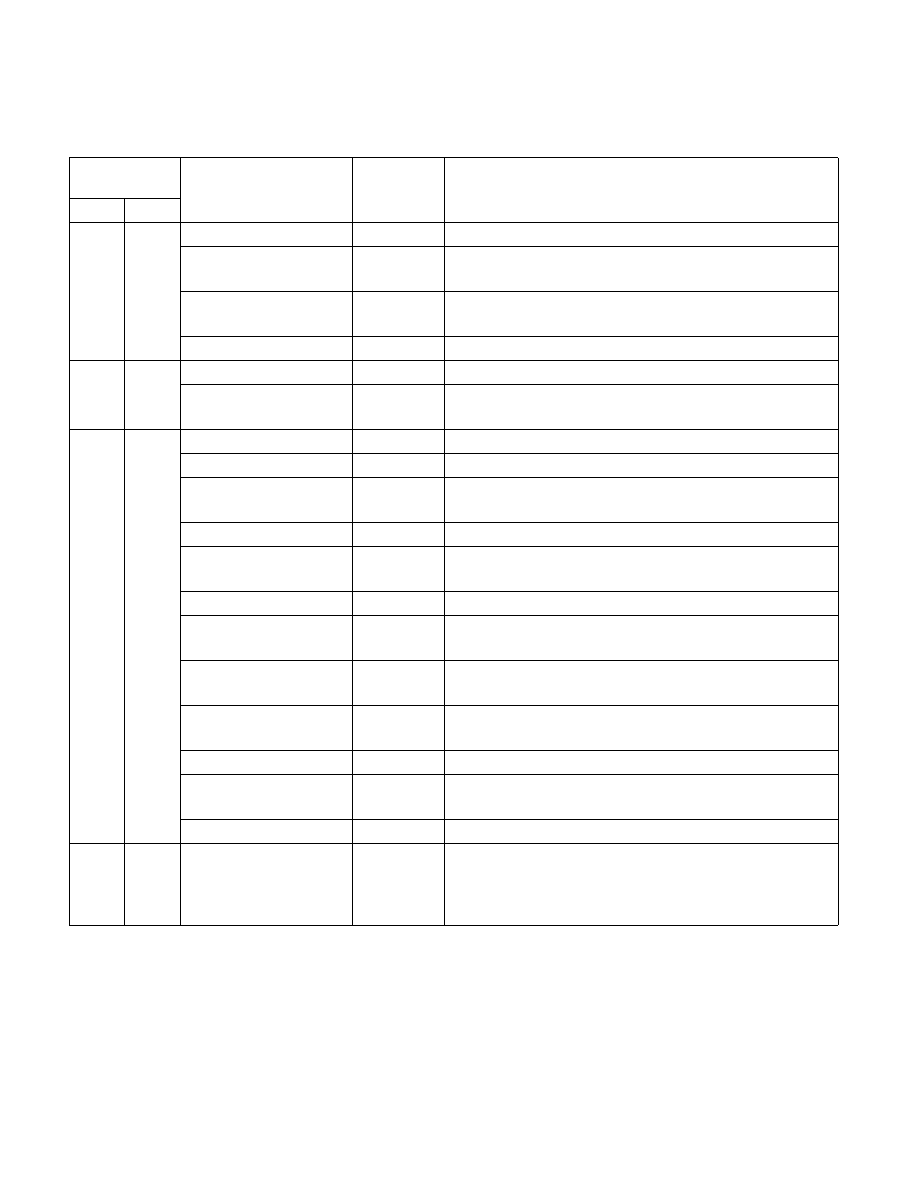

Table 35-34. Additional MSRs Common to Intel® Xeon® Processor D and Intel Xeon Processors E5 v4 Family Based

on the Broadwell Microarchitecture

Register

Address

Register Name

Scope

Bit Description

Hex

Dec

4EH

78

MSR_PPIN_CTL

Package

Protected Processor Inventory Number Enable Control (R/W)

0

LockOut (R/WO)

See Table 35-24.

1

Enable_PPIN (R/W)

See Table 35-24.

63:2

Reserved.

4FH

79

MSR_PPIN

Package

Protected Processor Inventory Number (R/O)

63:0

Protected Processor Inventory Number (R/O)

See Table 35-24.

CEH

206

MSR_PLATFORM_INFO

Package

See http://biosbits.org.

7:0

Reserved.

15:8

Package

Maximum Non-Turbo Ratio (R/O)

See Table 35-24.

22:16

Reserved.

23

Package

PPIN_CAP (R/O)

See Table 35-24.

27:24

Reserved.

28

Package

Programmable Ratio Limit for Turbo Mode (R/O)

See Table 35-24.

29

Package

Programmable TDP Limit for Turbo Mode (R/O)

See Table 35-24.

30

Package

Programmable TJ OFFSET (R/O)

See Table 35-24.

39:31

Reserved.

47:40

Package

Maximum Efficiency Ratio (R/O)

See Table 35-24.

63:48

Reserved.

E2H

226

MSR_PKG_CST_CONFIG_

CONTROL

Core

C-State Configuration Control (R/W)

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-states.

See http://biosbits.org.