Vol. 3C 35-223

MODEL-SPECIFIC REGISTERS (MSRS)

35.13 MSRS IN INTEL

®

CORE

™

M PROCESSORS AND 5TH GENERATION INTEL

CORE PROCESSORS

The Intel

®

Core™ M-5xxx processors and 5th generation Intel

®

Core™ Processors, and Intel

®

Xeon

®

Processor

E3-1200 v4 family are based on the Broadwell microarchitecture. The Intel

®

Core™ M-5xxx processors and 5th

generation Intel

®

Core™ Processors have CPUID DisplayFamily_DisplayModel signature 06_3DH. Intel

®

Xeon

®

Processor E3-1200 v4 family and the 5th generation Intel

®

Core™ Processors have CPUID

DisplayFamily_DisplayModel signature 06_47H. Processors with signatures 06_3DH and 06_47H support the MSR

interfaces listed in Table 35-18, Table 35-19, Table 35-20, Table 35-23, Table 35-27, Table 35-28, Table 35-32, and

Table 35-33. For an MSR listed in Table 35-33 that also appears in the model-specific tables of prior generations,

Table 35-33 supercede prior generation tables.

Table 35-32 lists MSRs that are common to processors based on the Broadwell microarchitectures (including CPUID

signatures 06_3DH, 06_47H, 06_4FH, and 06_56H).

F1BH

MSR_C17_PMON_CTR3

Package

Uncore C-box 17 perfmon counter 3.

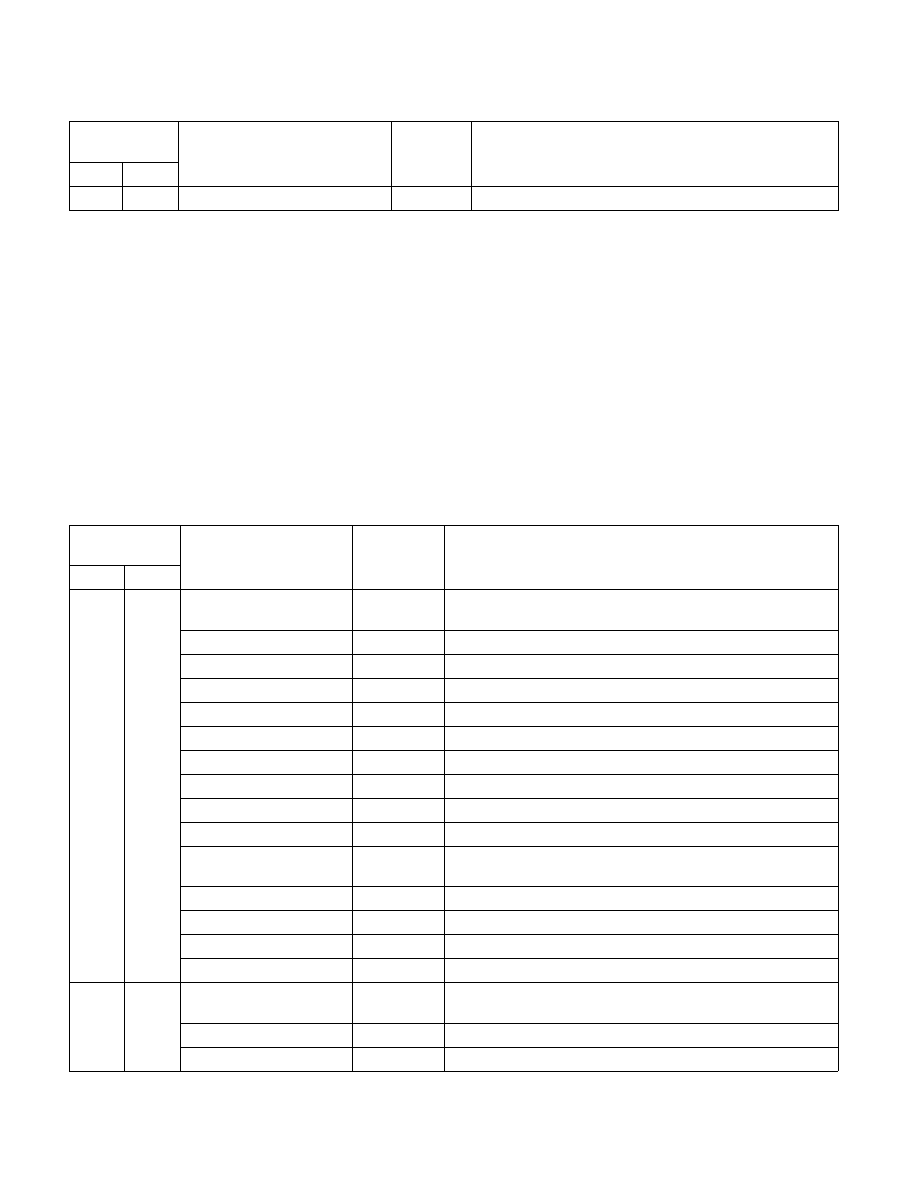

Table 35-32. Additional MSRs Common to Processors Based the Broadwell Microarchitectures

Register

Address

Register Name

Scope

Bit Description

Hex

Dec

38EH

910

IA32_PERF_GLOBAL_

STATUS

Thread

See Table 35-2. See Section 18.4.2, “Global Counter Control

0

Ovf_PMC0

1

Ovf_PMC1

2

Ovf_PMC2

3

Ovf_PMC3

31:4

Reserved.

32

Ovf_FixedCtr0

33

Ovf_FixedCtr1

34

Ovf_FixedCtr2

54:35

Reserved.

55

Trace_ToPA_PMI. See Section 36.2.6.2, “Table of Physical

60:56

Reserved.

61

Ovf_Uncore

62

Ovf_BufDSSAVE

63

CondChgd

390H

912

IA32_PERF_GLOBAL_OVF_

CTRL

Thread

See Table 35-2. See Section 18.4.2, “Global Counter Control

0

Set 1 to clear Ovf_PMC0

1

Set 1 to clear Ovf_PMC1

Table 35-31. Uncore PMU MSRs in Intel® Xeon® Processor E5 v3 Family (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec