Vol. 3C 35-3

MODEL-SPECIFIC REGISTERS (MSRS)

Architectural MSR or individual bit fields in an architectural MSR may be introduced or transitioned at the granu-

larity of certain processor family/model or the presence of certain CPUID feature flags. The right-most column of

Table 35-2 provides information on the introduction of each architectural MSR or its individual fields. This informa-

tion is expressed either as signature values of “DF_DM” (see Table 35-1) or via CPUID flags.

Certain bit field position may be related to the maximum physical address width, the value of which is expressed

as “

MAXPHYADDR” in Table 35-2. “MAXPHYADDR” is reported by CPUID.8000_0008H leaf.

MSR address range between 40000000H - 400000FFH is marked as a specially reserved range. All existing and

future processors will not implement any features using any MSR in this range.

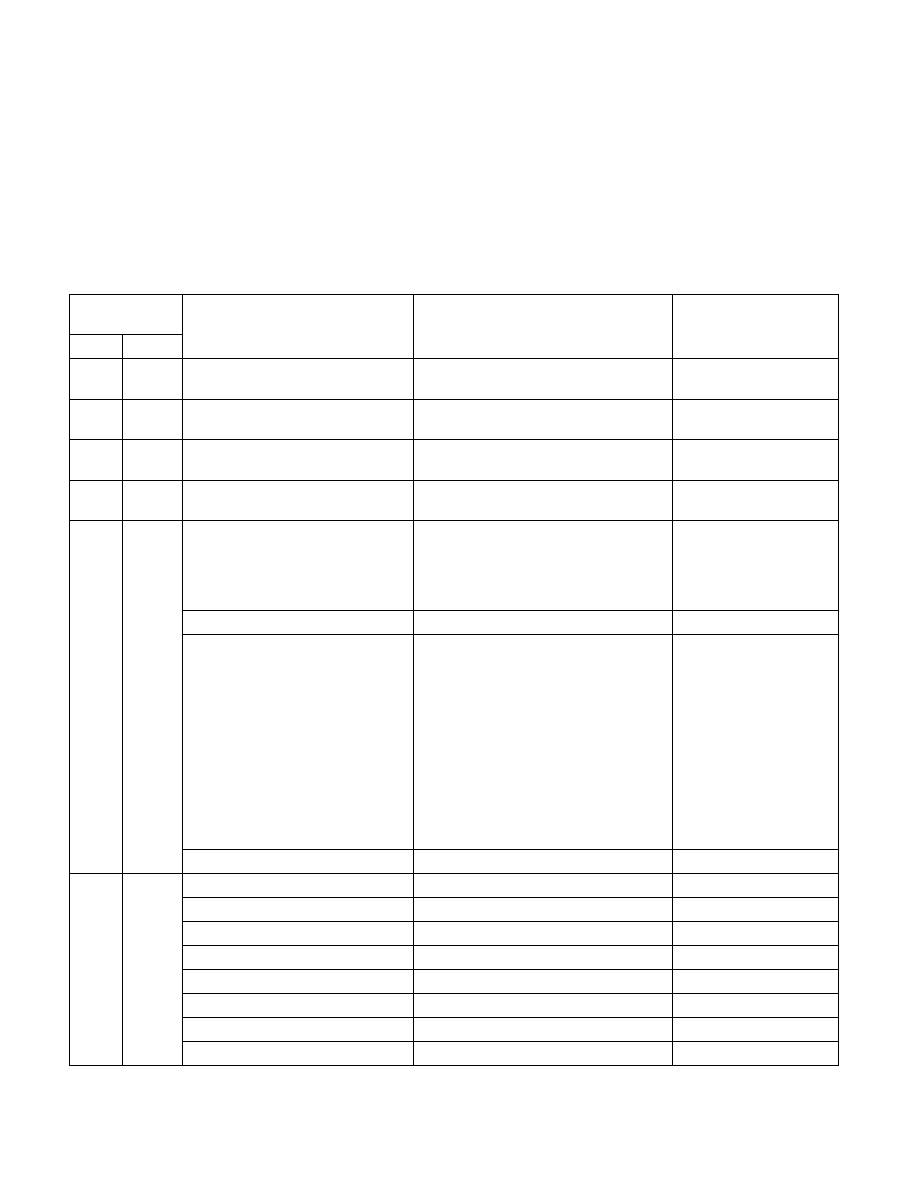

Table 35-2. IA-32 Architectural MSRs

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal

0H

0

IA32_P5_MC_ADDR (P5_MC_ADDR)

See Section 35.22, “MSRs in Pentium

Pentium Processor

(05_01H)

1H

1

IA32_P5_MC_TYPE (P5_MC_TYPE)

See Section 35.22, “MSRs in Pentium

DF_DM = 05_01H

6H

6

IA32_MONITOR_FILTER_SIZE

See Section 8.10.5, “Monitor/Mwait

0F_03H

10H

16

IA32_TIME_STAMP_

COUNTER (TSC)

See Section 17.15, “Time-Stamp Counter.”

05_01H

17H

23

IA32_PLATFORM_ID

(MSR_PLATFORM_ID )

Platform ID (RO)

The operating system can use this MSR to

determine “slot” information for the

processor and the proper microcode update

to load.

06_01H

49:0

Reserved.

52:50

Platform Id (RO)

Contains information concerning the

intended platform for the processor.

52 51 50

0 0 0 Processor

Flag

0

0 0 1 Processor

Flag

1

0 1 0 Processor

Flag

2

0 1 1 Processor

Flag

3

1 0 0 Processor

Flag

4

1 0 1 Processor

Flag

5

1 1 0 Processor

Flag

6

1 1 1 Processor

Flag

7

63:53

Reserved.

1BH

27

IA32_APIC_BASE (APIC_BASE)

06_01H

7:0

Reserved

8

BSP flag (R/W)

9

Reserved

10

Enable x2APIC mode

06_1AH

11

APIC Global Enable (R/W)

(MAXPHYADDR - 1):12

APIC Base (R/W)

63: MAXPHYADDR

Reserved