35-236 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

35.14.1 Additional MSRs Supported in the Intel® Xeon®

Processor D Product Family

The MSRs listed in Table 35-35 are available to Intel

®

Xeon

®

Processor D Product Family (CPUID

DisplayFamily_DisplayModel = 06_56H). The Intel

®

Xeon

®

processor D product family is based on the Broadwell

microarchitecture and supports the MSR interfaces listed in Table 35-18, Table 35-27, Table 35-32, Table 35-34,

and Table 35-35.

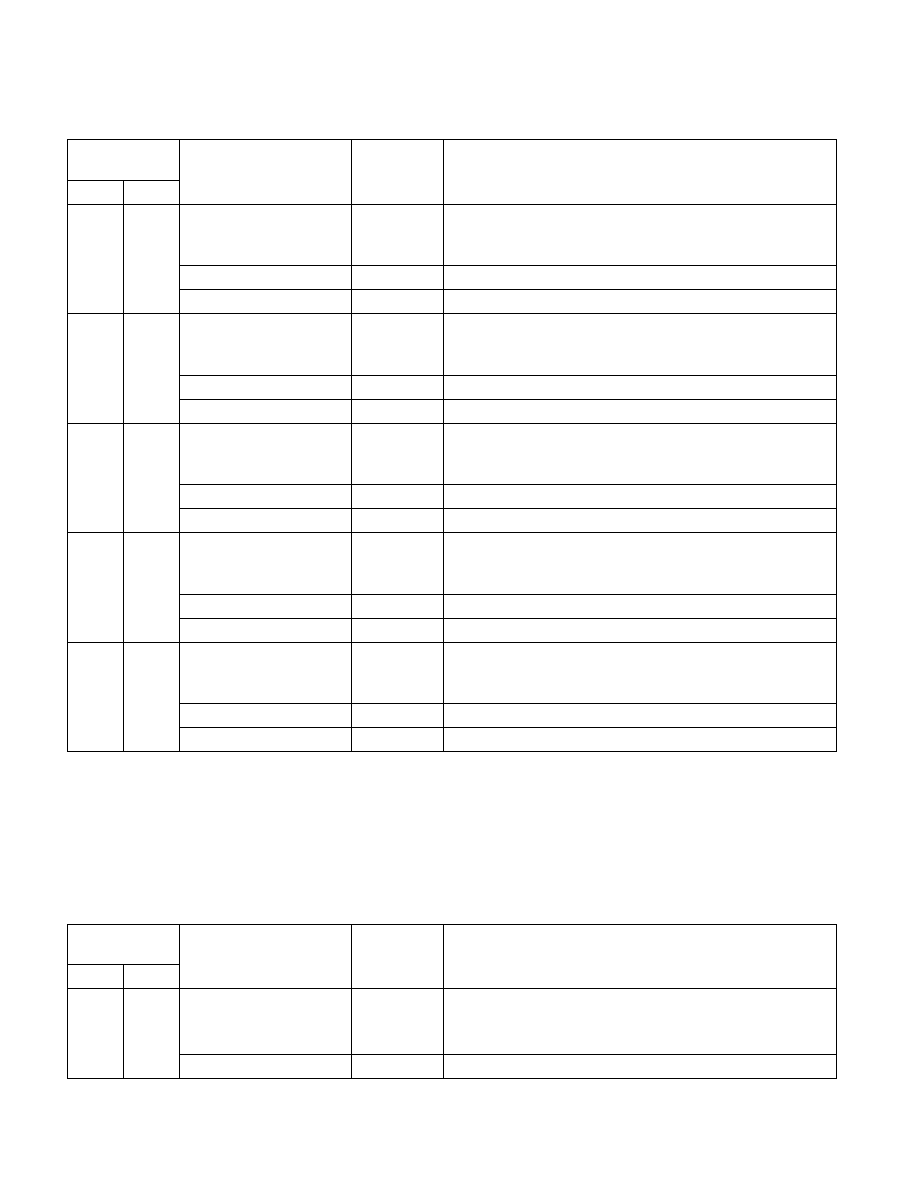

C9BH

3227

IA32_L3_QOS_MASK_11

Package

L3 Class Of Service Mask - COS 11 (R/W).

if CPUID.(EAX=10H, ECX=1):EDX.COS_MAX[15:0]

>=11

0:19

CBM: Bit vector of available L3 ways for COS 11 enforcement

63:20

Reserved

C9CH

3228

IA32_L3_QOS_MASK_12

Package

L3 Class Of Service Mask - COS 12 (R/W).

if CPUID.(EAX=10H, ECX=1):EDX.COS_MAX[15:0]

>=12

0:19

CBM: Bit vector of available L3 ways for COS 12 enforcement

63:20

Reserved

C9DH

3229

IA32_L3_QOS_MASK_13

Package

L3 Class Of Service Mask - COS 13 (R/W).

if CPUID.(EAX=10H, ECX=1):EDX.COS_MAX[15:0]

>=13

0:19

CBM: Bit vector of available L3 ways for COS 13 enforcement

63:20

Reserved

C9EH

3230

IA32_L3_QOS_MASK_14

Package

L3 Class Of Service Mask - COS 14 (R/W).

if CPUID.(EAX=10H, ECX=1):EDX.COS_MAX[15:0]

>=14

0:19

CBM: Bit vector of available L3 ways for COS 14 enforcement

63:20

Reserved

C9FH

3231

IA32_L3_QOS_MASK_15

Package

L3 Class Of Service Mask - COS 15 (R/W).

if CPUID.(EAX=10H, ECX=1):EDX.COS_MAX[15:0]

>=15

0:19

CBM: Bit vector of available L3 ways for COS 15 enforcement

63:20

Reserved

Table 35-35. Additional MSRs Supported by Intel® Xeon® Processor D with DisplayFamily_DisplayModel 06_56H

Register

Address

Register Name

Scope

Bit Description

Hex

Dec

1ACH

428

MSR_TURBO_RATIO_LIMIT3 Package

Config Ratio Limit of Turbo Mode

RO if MSR_PLATFORM_INFO.[28] = 0,

RW if MSR_PLATFORM_INFO.[28] = 1

62:0

Package

Reserved

Table 35-34. Additional MSRs Common to Intel® Xeon® Processor D and Intel Xeon Processors E5 v4 Family Based

on the Broadwell Microarchitecture

Register

Address

Register Name

Scope

Bit Description

Hex

Dec