35-226 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

35.14 MSRS IN INTEL

®

XEON

®

PROCESSORS E5 V4 FAMILY

The MSRs listed in Table 35-34 are available and common to Intel

®

Xeon

®

Processor D product Family (CPUID

DisplayFamily_DisplayModel = 06_56H) and to Intel Xeon processors E5 v4, E7 v4 families (CPUID

DisplayFamily_DisplayModel = 06_4FH). They are based on the Broadwell microarchitecture.

See Section 35.14.1 for lists of tables of MSRs that are supported by Intel

®

Xeon

®

Processor D Family.

14:11

Reserved

15

CFG Lock (R/WO)

24:16

Reserved

25

C3 State Auto Demotion Enable (R/W)

26

C1 State Auto Demotion Enable (R/W)

27

Enable C3 Undemotion (R/W)

28

Enable C1 Undemotion (R/W)

29

Enable Package C-State Auto-demotion (R/W)

30

Enable Package C-State Undemotion (R/W)

63:31

Reserved

1ADH

429

MSR_TURBO_RATIO_LIMIT

Package

Maximum Ratio Limit of Turbo Mode

RO if MSR_PLATFORM_INFO.[28] = 0,

RW if MSR_PLATFORM_INFO.[28] = 1

7:0

Package

Maximum Ratio Limit for 1C

Maximum turbo ratio limit of 1 core active.

15:8

Package

Maximum Ratio Limit for 2C

Maximum turbo ratio limit of 2 core active.

23:16

Package

Maximum Ratio Limit for 3C

Maximum turbo ratio limit of 3 core active.

31:24

Package

Maximum Ratio Limit for 4C

Maximum turbo ratio limit of 4 core active.

39:32

Package

Maximum Ratio Limit for 5C

Maximum turbo ratio limit of 5core active.

47:40

Package

Maximum Ratio Limit for 6C

Maximum turbo ratio limit of 6core active.

63:48

Reserved.

639H

1593

MSR_PP0_ENERGY_STATUS Package

PP0 Energy Status (R/O)

See Section 14.9.4, “PP0/PP1 RAPL Domains.”

See Table 35-18, Table 35-19, Table 35-20, Table 35-23, Table 35-27, Table 35-28, Table 35-32 for other MSR definitions applicable

to processors with CPUID signature 06_3DH.

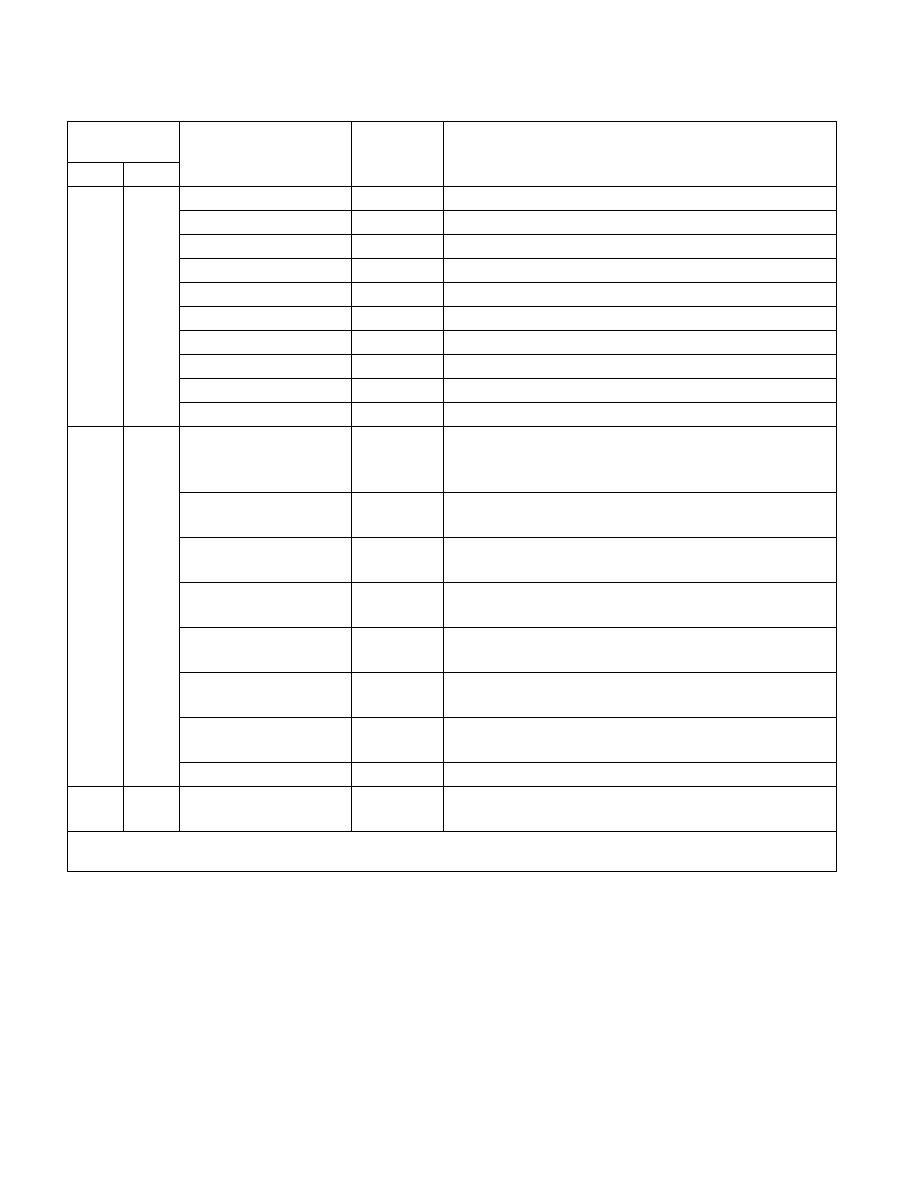

Table 35-33. Additional MSRs Supported by Intel® Core™ M Processors and 5th Generation Intel® Core™ Processors

Register

Address

Register Name

Scope

Bit Description

Hex

Dec