Vol. 3B 14-35

POWER AND THERMAL MANAGEMENT

ŌĆó

Maximum Time Window (bits 53:48): The unsigned integer value is the equivalent of largest acceptable

value to program the time window of MSR_PKG_POWER_LIMIT. The unit of this field is specified by the ŌĆ£Time

UnitsŌĆØ field of MSR_RAPL_POWER_UNIT.

MSR_PKG_PERF_STATUS is a read-only MSR. It reports the total time for which the package was throttled due to

the RAPL power limits. Throttling in this context is defined as going below the OS-requested P-state or T-state. It

has a wrap-around time of many hours. The availability of this MSR is platform specific (see Chapter 35).

ŌĆó

Accumulated Package Throttled Time (bits 31:0): The unsigned integer value represents the cumulative

time (since the last time this register is cleared) that the package has throttled. The unit of this field is specified

by the ŌĆ£Time UnitsŌĆØ field of MSR_RAPL_POWER_UNIT.

14.9.4

PP0/PP1 RAPL Domains

The MSR interfaces defined for the PP0 and PP1 domains are identical in layout. Generally, PP0 refers to the

processor cores. The availability of PP1 RAPL domain interface is platform-specific. For a client platform, the PP1

domain refers to the power plane of a specific device in the uncore. For server platforms, the PP1 domain is not

supported, but its PP0 domain supports the MSR_PP0_PERF_STATUS interface.

ŌĆó

MSR_PP0_POWER_LIMIT/MSR_PP1_POWER_LIMIT allow software to set power limits for the respective power

plane domain.

ŌĆó

MSR_PP0_ENERGY_STATUS/MSR_PP1_ENERGY_STATUS report actual energy usage on a power plane.

ŌĆó

MSR_PP0_POLICY/MSR_PP1_POLICY allow software to adjust balance for respective power plane.

MSR_PP0_PERF_STATUS can report the performance impact of power limiting, but it is not available in client plat-

forms.

MSR_PP0_POWER_LIMIT/MSR_PP1_POWER_LIMIT allow a software agent to define power limitation for the

respective power plane domain. A lock mechanism in each power plane domain allows the software agent to

enforce power limit settings independently. Once a lock bit is set, the power limit settings in that power plane are

static and un-modifiable until next RESET.

The bit fields of MSR_PP0_POWER_LIMIT/MSR_PP1_POWER_LIMIT (Figure 14-36) are:

ŌĆó

Power Limit (bits 14:0): Sets the average power usage limit of the respective power plane domain. The unit

of this field is specified by the ŌĆ£Power UnitsŌĆØ field of MSR_RAPL_POWER_UNIT.

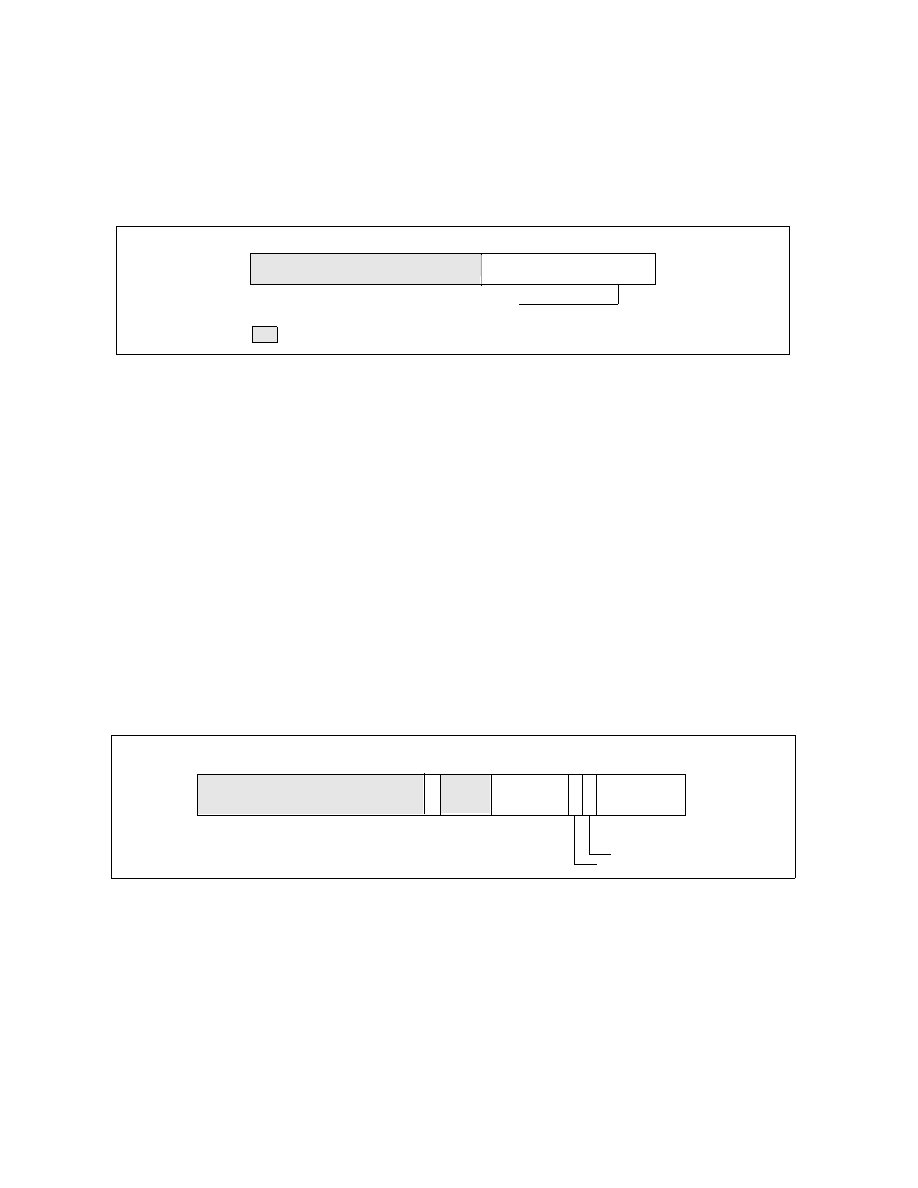

Figure 14-35. MSR_PKG_PERF_STATUS MSR

Figure 14-36. MSR_PP0_POWER_LIMIT/MSR_PP1_POWER_LIMIT Register

63

0

Reserved

Accumulated pkg throttled time

31

32

Reserved

63

Enable limit

Clamping limit

30

24 23

15

0

Power Limit

31

32

14

L

O

C

16

17

K

Time window

Power Limit