Vol. 3C 35-163

MODEL-SPECIFIC REGISTERS (MSRS)

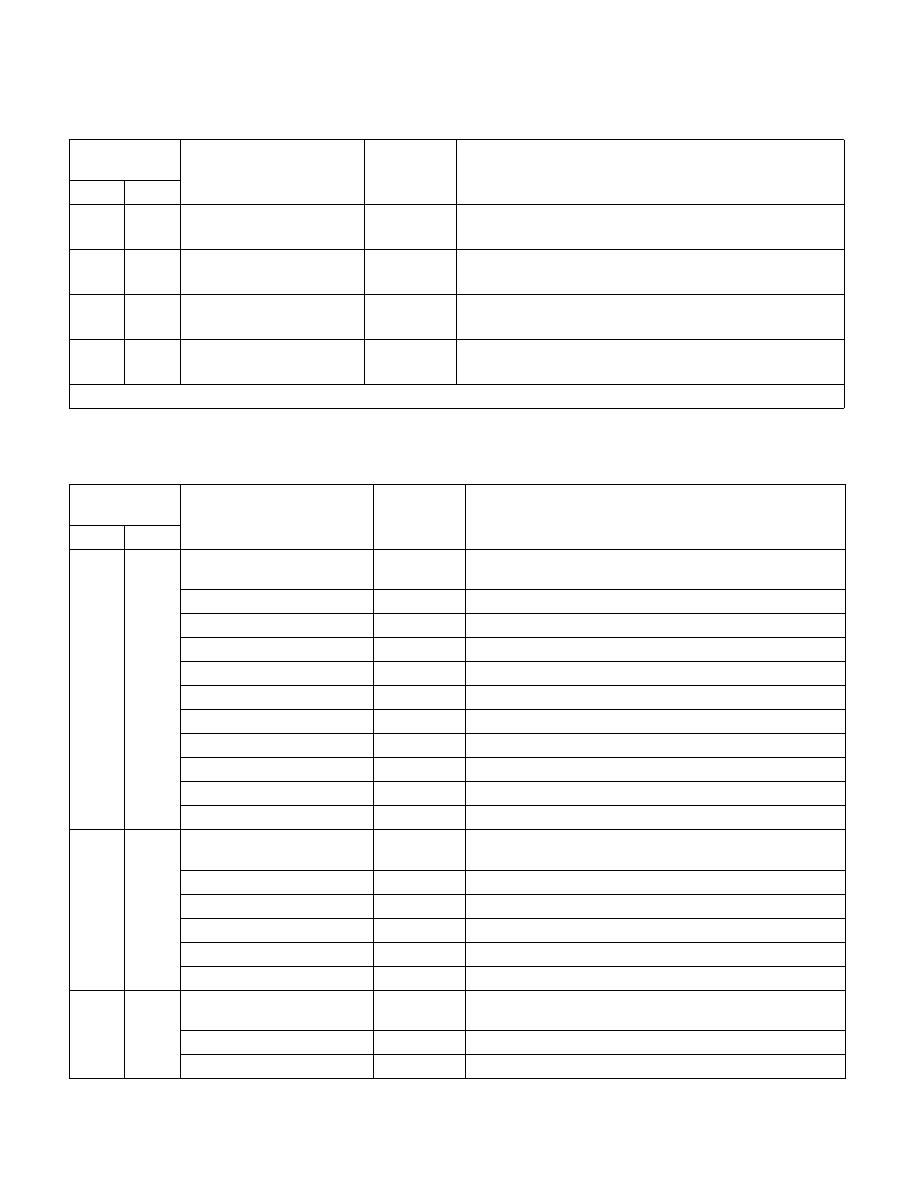

Table 35-20 lists the MSRs of uncore PMU for Intel processors with CPUID signature 06_2AH.

63AH

1594

MSR_PP0_POLICY

Package

PP0 Balance Policy (R/W)

See Section 14.9.4, “PP0/PP1 RAPL Domains.”

640H

1600

MSR_PP1_POWER_LIMIT

Package

PP1 RAPL Power Limit Control (R/W)

See Section 14.9.4, “PP0/PP1 RAPL Domains.”

641H

1601

MSR_PP1_ENERGY_STATUS

Package

PP1 Energy Status (R/O)

See Section 14.9.4, “PP0/PP1 RAPL Domains.”

642H

1602

MSR_PP1_POLICY

Package

PP1 Balance Policy (R/W)

See Section 14.9.4, “PP0/PP1 RAPL Domains.”

See Table 35-18, Table 35-19, and Table 35-20 for MSR definitions applicable to processors with CPUID signature 06_2AH.

Table 35-20. Uncore PMU MSRs Supported by 2nd Generation Intel® Core™ Processors

Register

Address

Register Name

Scope

Bit Description

Hex

Dec

391H

913

MSR_UNC_PERF_GLOBAL_

CTRL

Package

Uncore PMU global control

0

Slice 0 select

1

Slice 1 select

2

Slice 2 select

3

Slice 3 select

4

Slice 4 select

18:5

Reserved.

29

Enable all uncore counters

30

Enable wake on PMI

31

Enable Freezing counter when overflow

63:32

Reserved.

392H

914

MSR_UNC_PERF_GLOBAL_

STATUS

Package

Uncore PMU main status

0

Fixed counter overflowed

1

An ARB counter overflowed

2

Reserved

3

A CBox counter overflowed (on any slice)

63:4

Reserved.

394H

916

MSR_UNC_PERF_FIXED_

CTRL

Package

Uncore fixed counter control (R/W)

19:0

Reserved

20

Enable overflow propagation

Table 35-19. MSRs Supported by 2nd Generation Intel® Core™ Processors (Intel® microarchitecture code name Sandy

Bridge) (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec