24-6 Vol. 3C

VIRTUAL MACHINE CONTROL STRUCTURES

ÔÇö 1: HLT. The logical processor is inactive because it executed the HLT instruction.

ÔÇö 2: Shutdown. The logical processor is inactive because it incurred a triple fault

1

or some other serious

error.

ÔÇö 3: Wait-for-SIPI. The logical processor is inactive because it is waiting for a startup-IPI (SIPI).

Future processors may include support for other activity states. Software should read the VMX capability MSR

IA32_VMX_MISC (see Appendix A.6) to determine what activity states are supported.

ÔÇó

Interruptibility state (32 bits). The IA-32 architecture includes features that permit certain events to be

blocked for a period of time. This field contains information about such blocking. Details and the format of this

field are given in Table 24-3.

ÔÇó

Pending debug exceptions (64 bits; 32 bits on processors that do not support Intel 64 architecture). IA-32

processors may recognize one or more debug exceptions without immediately delivering them.

2

This field

contains information about such exceptions. This field is described in Table 24-4.

2. Execution of the MWAIT instruction may put a logical processor into an inactive state. However, this VMCS field never reflects this

state. See Section 27.1.

1. A triple fault occurs when a logical processor encounters an exception while attempting to deliver a double fault.

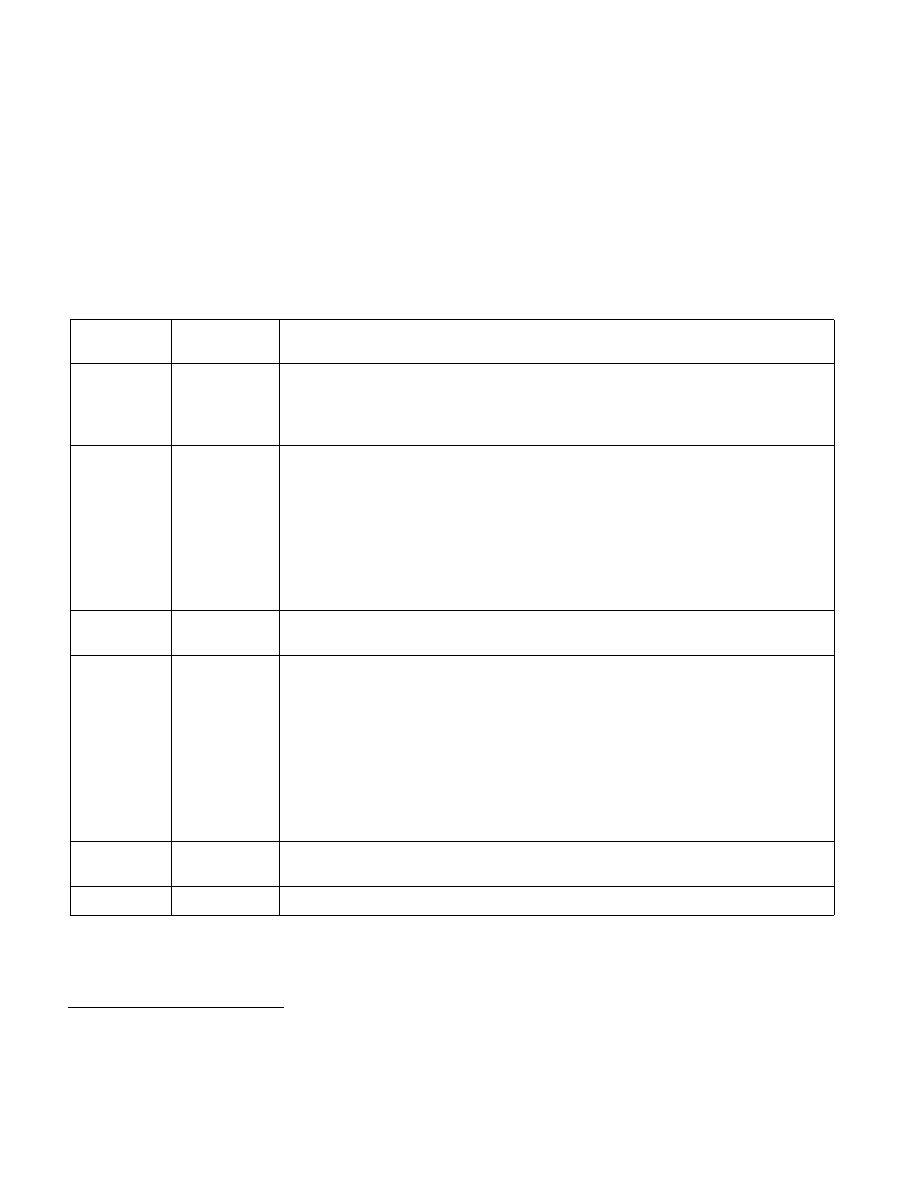

Table 24-3. Format of Interruptibility State

Bit

Position(s)

Bit Name

Notes

0

Blocking by STI

See the ÔÇťSTIÔÇöSet Interrupt FlagÔÇŁ section in Chapter 4 of the Intel┬« 64 and IA-32 Architectures

Software DeveloperÔÇÖs Manual, Volume 2B.

Execution of STI with RFLAGS.IF = 0 blocks interrupts (and, optionally, other events) for one

instruction after its execution. Setting this bit indicates that this blocking is in effect.

1

Blocking by

MOV SS

See the ÔÇťMOVÔÇöMove a Value from the StackÔÇŁ from Chapter 4 of the Intel┬« 64 and IA-32

Architectures Software DeveloperÔÇÖs Manual, Volume 2B, and ÔÇťPOPÔÇöPop a Value from the

StackÔÇŁ from Chapter 4 of the Intel┬« 64 and IA-32 Architectures Software DeveloperÔÇÖs Manual,

Volume 2B, and Section 6.8.3 in the Intel┬« 64 and IA-32 Architectures Software DeveloperÔÇÖs

Manual, Volume 3A.

Execution of a MOV to SS or a POP to SS blocks interrupts for one instruction after its

execution. In addition, certain debug exceptions are inhibited between a MOV to SS or a POP to

SS and a subsequent instruction. Setting this bit indicates that the blocking of all these events

is in effect. This document uses the term ÔÇťblocking by MOV SS,ÔÇŁ but it applies equally to POP SS.

2

Blocking by SMI

See Section 34.2. System-management interrupts (SMIs) are disabled while the processor is in

system-management mode (SMM). Setting this bit indicates that blocking of SMIs is in effect.

3

Blocking by NMI

See Section 6.7.1 in the Intel┬« 64 and IA-32 Architectures Software DeveloperÔÇÖs Manual,

Volume 3A and Section 34.8.

Delivery of a non-maskable interrupt (NMI) or a system-management interrupt (SMI) blocks

subsequent NMIs until the next execution of IRET. See Section 25.3 for how this behavior of

IRET may change in VMX non-root operation. Setting this bit indicates that blocking of NMIs is

in effect. Clearing this bit does not imply that NMIs are not (temporarily) blocked for other

reasons.

If the ÔÇťvirtual NMIsÔÇŁ VM-execution control (see Section 24.6.1) is 1, this bit does not control the

blocking of NMIs. Instead, it refers to ÔÇťvirtual-NMI blockingÔÇŁ (the fact that guest software is not

ready for an NMI).

4

Enclave

interruption

A VM exit saves this bit as 1 to indicate that the VM exit was incident to enclave mode.

31:5

Reserved

VM entry will fail if these bits are not 0. See Section 26.3.1.5.