Vol. 3C 34-13

SYSTEM MANAGEMENT MODE

34.8

NMI HANDLING WHILE IN SMM

NMI interrupts are blocked upon entry to the SMI handler. If an NMI request occurs during the SMI handler, it is

latched and serviced after the processor exits SMM. Only one NMI request will be latched during the SMI handler.

If an NMI request is pending when the processor executes the RSM instruction, the NMI is serviced before the next

instruction of the interrupted code sequence. This assumes that NMIs were not blocked before the SMI occurred. If

NMIs were blocked before the SMI occurred, they are blocked after execution of RSM.

Although NMI requests are blocked when the processor enters SMM, they may be enabled through software by

executing an IRET instruction. If the SMI handler requires the use of NMI interrupts, it should invoke a dummy

interrupt service routine for the purpose of executing an IRET instruction. Once an IRET instruction is executed,

NMI interrupt requests are serviced in the same “real mode” manner in which they are handled outside of SMM.

A special case can occur if an SMI handler nests inside an NMI handler and then another NMI occurs. During NMI

interrupt handling, NMI interrupts are disabled, so normally NMI interrupts are serviced and completed with an

IRET instruction one at a time. When the processor enters SMM while executing an NMI handler, the processor

saves the SMRAM state save map but does not save the attribute to keep NMI interrupts disabled. Potentially, an

NMI could be latched (while in SMM or upon exit) and serviced upon exit of SMM even though the previous NMI

handler has still not completed. One or more NMIs could thus be nested inside the first NMI handler. The NMI inter-

rupt handler should take this possibility into consideration.

Also, for the Pentium processor, exceptions that invoke a trap or fault handler will enable NMI interrupts from inside

of SMM. This behavior is implementation specific for the Pentium processor and is not part of the IA-32 architec-

ture.

34.9

SMM REVISION IDENTIFIER

The SMM revision identifier field is used to indicate the version of SMM and the SMM extensions that are supported

by the processor (see Figure 34-2). The SMM revision identifier is written during SMM entry and can be examined

in SMRAM space at offset 7EFCH. The lower word of the SMM revision identifier refers to the version of the base

SMM architecture.

The upper word of the SMM revision identifier refers to the extensions available. If the I/O instruction restart flag

(bit 16) is set, the processor supports the I/O instruction restart (see Section 34.12); if the SMBASE relocation flag

(bit 17) is set, SMRAM base address relocation is supported (see Section 34.11).

34.10 AUTO

HALT

RESTART

If the processor is in a HALT state (due to the prior execution of a HLT instruction) when it receives an SMI, the

processor records the fact in the auto HALT restart flag in the saved processor state (see Figure 34-3). (This flag is

located at offset 7F02H and bit 0 in the state save area of the SMRAM.)

If the processor sets the auto HALT restart flag upon entering SMM (indicating that the SMI occurred when the

processor was in the HALT state), the SMI handler has two options:

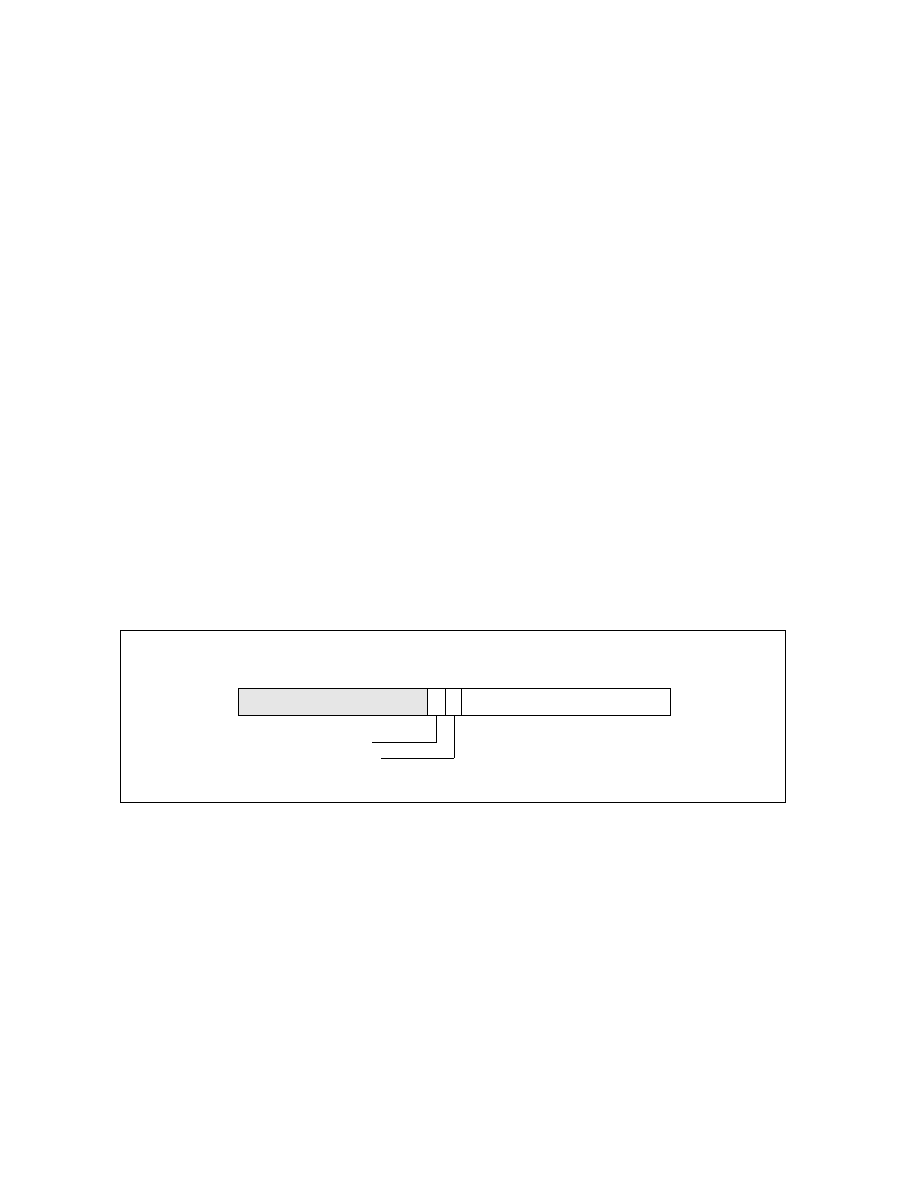

Figure 34-2. SMM Revision Identifier

SMM Revision Identifier

I/O Instruction Restart

SMBASE Relocation

Register Offset

7EFCH

31

0

Reserved

18 17 16 15