Vol. 3C 24-7

VIRTUAL MACHINE CONTROL STRUCTURES

ÔÇó

VMCS link pointer (64 bits). If the ÔÇťVMCS shadowingÔÇŁ VM-execution control is 1, the VMREAD and VMWRITE

instructions access the VMCS referenced by this pointer (see Section 24.10). Otherwise, software should set

this field to FFFFFFFF_FFFFFFFFH to avoid VM-entry failures (see Section 26.3.1.5).

ÔÇó

VMX-preemption timer value (32 bits). This field is supported only on processors that support the 1-setting

of the ÔÇťactivate VMX-preemption timerÔÇŁ VM-execution control. This field contains the value that the VMX-

preemption timer will use following the next VM entry with that setting. See Section 25.5.1 and Section 26.6.4.

ÔÇó

Page-directory-pointer-table entries (PDPTEs; 64 bits each). These four (4) fields (PDPTE0, PDPTE1,

PDPTE2, and PDPTE3) are supported only on processors that support the 1-setting of the ÔÇťenable EPTÔÇŁ VM-

execution control. They correspond to the PDPTEs referenced by CR3 when PAE paging is in use (see Section

4.4 in the Intel┬« 64 and IA-32 Architectures Software DeveloperÔÇÖs Manual, Volume 3A). They are used only if

the ÔÇťenable EPTÔÇŁ VM-execution control is 1.

ÔÇó

Guest interrupt status (16 bits). This field is supported only on processors that support the 1-setting of the

ÔÇťvirtual-interrupt deliveryÔÇŁ VM-execution control. It characterizes part of the guestÔÇÖs virtual-APIC state and

does not correspond to any processor or APIC registers. It comprises two 8-bit subfields:

ÔÇö Requesting virtual interrupt (RVI). This is the low byte of the guest interrupt status. The processor

treats this value as the vector of the highest priority virtual interrupt that is requesting service. (The value

0 implies that there is no such interrupt.)

ÔÇö Servicing virtual interrupt (SVI). This is the high byte of the guest interrupt status. The processor

treats this value as the vector of the highest priority virtual interrupt that is in service. (The value 0 implies

that there is no such interrupt.)

2. For example, execution of a MOV to SS or a POP to SS may inhibit some debug exceptions for one instruction. See Section 6.8.3 of

Intel┬« 64 and IA-32 Architectures Software DeveloperÔÇÖs Manual, Volume 3A. In addition, certain events incident to an instruction

(for example, an INIT signal) may take priority over debug traps generated by that instruction. See Table 6-2 in the Intel® 64 and

IA-32 Architectures Software DeveloperÔÇÖs Manual, Volume 3A.

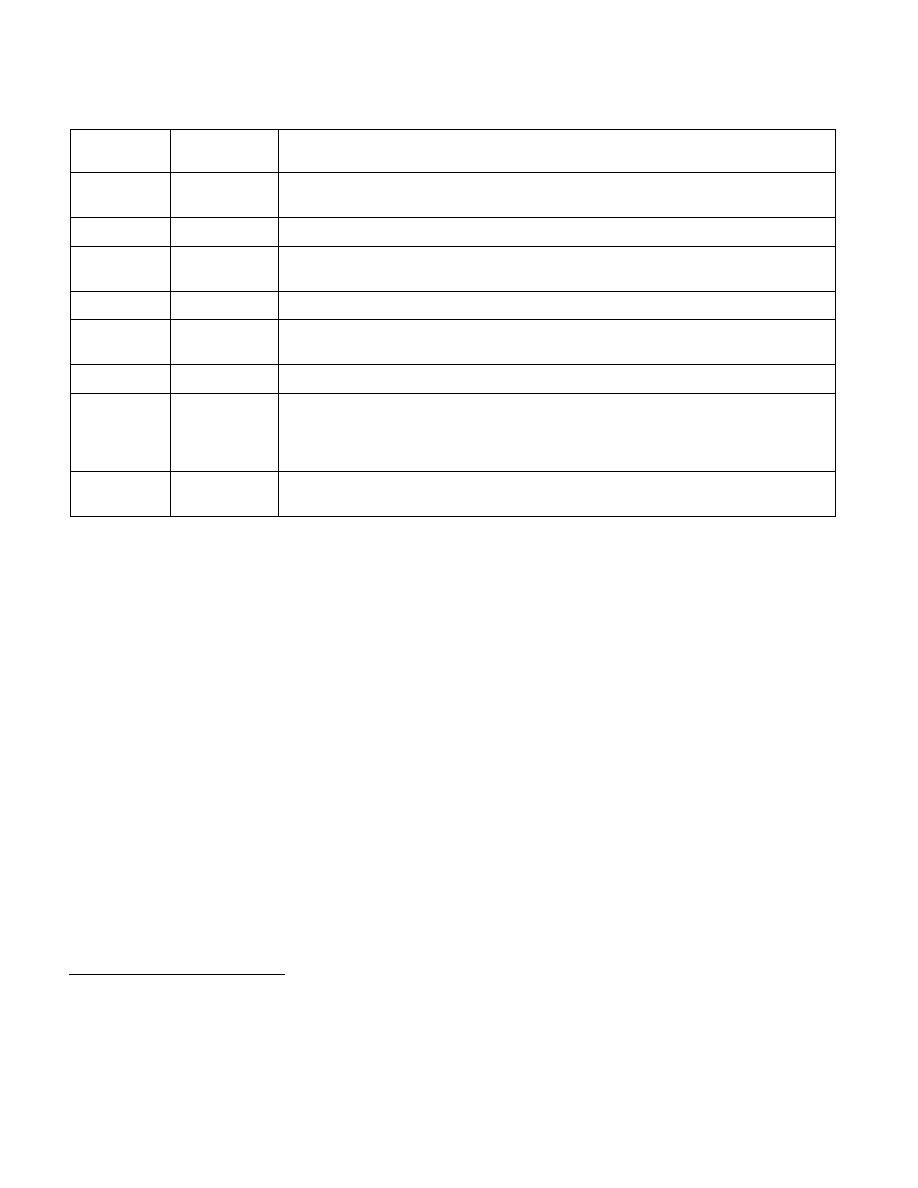

Table 24-4. Format of Pending-Debug-Exceptions

Bit

Position(s)

Bit Name

Notes

3:0

B3 ÔÇô B0

When set, each of these bits indicates that the corresponding breakpoint condition was met.

Any of these bits may be set even if the corresponding enabling bit in DR7 is not set.

11:4

Reserved

VM entry fails if these bits are not 0. See Section 26.3.1.5.

12

Enabled

breakpoint

When set, this bit indicates that at least one data or I/O breakpoint was met and was enabled in

DR7.

13

Reserved

VM entry fails if this bit is not 0. See Section 26.3.1.5.

14

BS

When set, this bit indicates that a debug exception would have been triggered by single-step

execution mode.

15

Reserved

VM entry fails if this bit is not 0. See Section 26.3.1.5.

16

RTM

When set, this bit indicates that a debug exception (#DB) or a breakpoint exception (#BP)

occurred inside an RTM region while advanced debugging of RTM transactional regions was

enabled (see Section 16.3.7, ÔÇťRTM-Enabled Debugger Support,ÔÇŁ of Intel┬« 64 and IA-32

Architectures Software DeveloperÔÇÖs Manual, Volume 1).

1

63:17

Reserved

VM entry fails if these bits are not 0. See Section 26.3.1.5. Bits 63:32 exist only on processors

that support Intel 64 architecture.

NOTES:

1. In general, the format of this field matches that of DR6. However, DR6 clears bit 16 to indicate an RTM-related exception, while this

field sets the bit to indicate that condition.