17-22 Vol. 3B

DEBUG, BRANCH PROFILE, TSC, AND RESOURCE MONITORING FEATURES

Fields in the buffer management area of a DS save area are described in Section 17.4.9.

The format of a branch trace record and a PEBS record are the same as the 64-bit record formats shown in Figures

17-9 and Figures 17-10, with the exception that the branch predicted bit is not supported by Intel Core microarchi-

tecture or Intel Atom microarchitecture. The 64-bit record formats for BTS and PEBS apply to DS save area for all

operating modes.

The procedures used to program IA32_DEBUGCTL MSR to set up a BTS buffer or a CPL-qualified BTS are described

in Section 17.4.9.3 and Section 17.4.9.4.

Required elements for writing a DS interrupt service routine are largely the same on processors that support using

DS Save area for BTS or PEBS records. However, on processors based on Intel NetBurst

®

microarchitecture, re-

enabling counting requires writing to CCCRs. But a DS interrupt service routine on processors supporting architec-

tural performance monitoring should:

•

Re-enable the enable bits in IA32_PERF_GLOBAL_CTRL MSR if it is servicing an overflow PMI due to PEBS.

•

Clear overflow indications by writing to IA32_PERF_GLOBAL_OVF_CTRL when a counting configuration is

changed. This includes bit 62 (ClrOvfBuffer) and the overflow indication of counters used in either PEBS or

general-purpose counting (specifically: bits 0 or 1; see Figures 18-3).

17.4.9.2 Setting Up the DS Save Area

To save branch records with the BTS buffer, the DS save area must first be set up in memory as described in the

following procedure (See Section 18.4.4.1, “Setting up the PEBS Buffer,” for instructions for setting up a PEBS

buffer, respectively, in the DS save area):

1. Create the DS buffer management information area in memory (see Section 17.4.9, “BTS and DS Save Area,”

and Section 17.4.9.1, “64 Bit Format of the DS Save Area”). Also see the additional notes in this section.

2. Write the base linear address of the DS buffer management area into the IA32_DS_AREA MSR.

3. Set up the performance counter entry in the xAPIC LVT for fixed delivery and edge sensitive. See Section

4. Establish an interrupt handler in the IDT for the vector associated with the performance counter entry in the

xAPIC LVT.

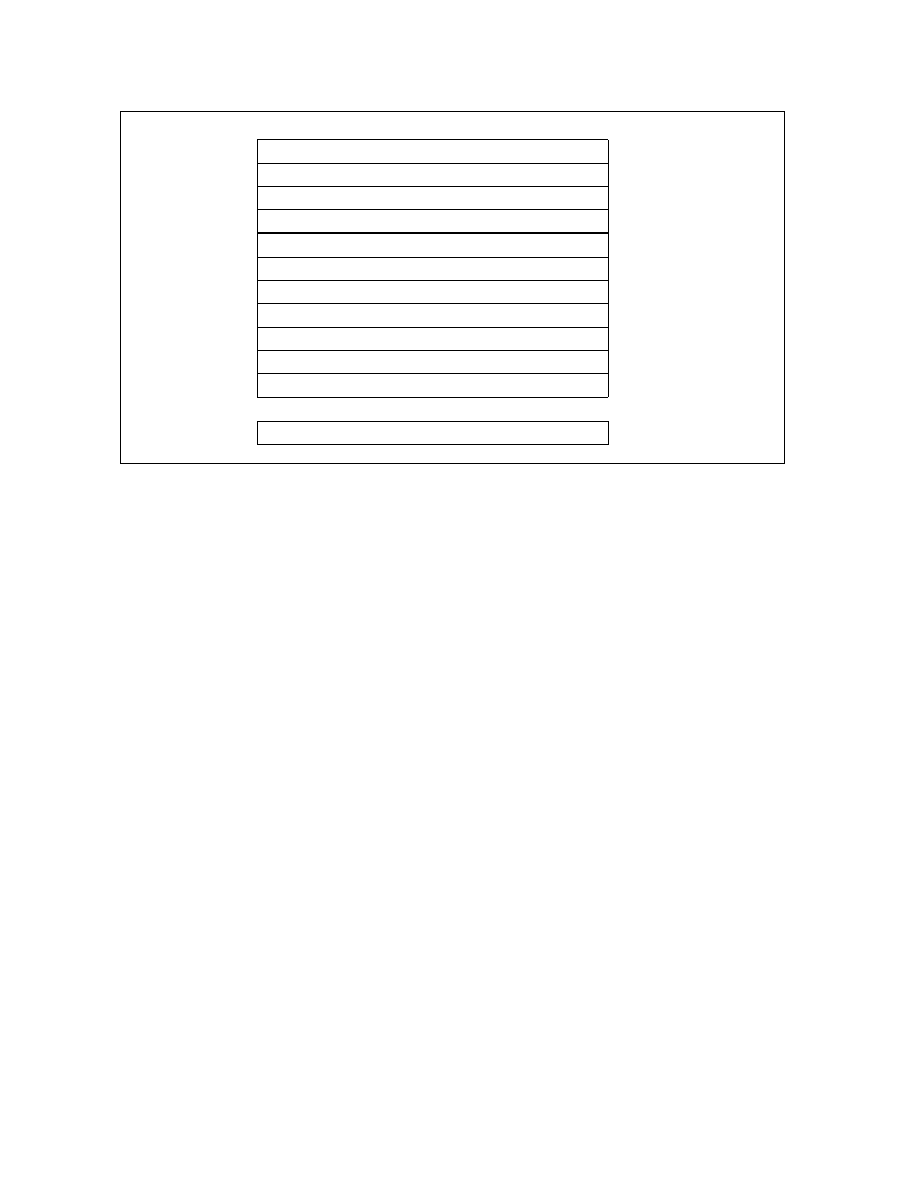

Figure 17-10. 64-bit PEBS Record Format

RFLAGS

0H

8H

10H

0

63

RIP

20H

30H

28H

38H

40H

48H

18H

RAX

RBX

RCX

RDX

RSI

RDI

RBP

RSP

R8

...

R15

50H

...

88H