17-24 Vol. 3B

DEBUG, BRANCH PROFILE, TSC, AND RESOURCE MONITORING FEATURES

NOTES

If the buffer size is set to less than the minimum allowable value (i.e. BTS absolute maximum < 1

+ size of BTS record), the results of BTS is undefined.

In order to prevent generating an interrupt, when working with circular BTS buffer, SW need to set

BTS interrupt threshold to a value greater than BTS absolute maximum (fields of the DS buffer

management area). It's not enough to clear the BTINT flag itself only.

17.4.9.4 Setting Up CPL-Qualified BTS

If the processor supports CPL-qualified last branch recording mechanism, the generation of branch records and

storing of them in the BTS buffer are determined by: TR, BTS, BTS_OFF_OS, BTS_OFF_USR, and BTINT. The

encoding of these five bits are shown in Table 17-6.

17.4.9.5 Writing the DS Interrupt Service Routine

The BTS, non-precise event-based sampling, and PEBS facilities share the same interrupt vector and interrupt

service routine (called the debug store interrupt service routine or DS ISR). To handle BTS, non-precise event-

based sampling, and PEBS interrupts: separate handler routines must be included in the DS ISR. Use the following

guidelines when writing a DS ISR to handle BTS, non-precise event-based sampling, and/or PEBS interrupts.

•

The DS interrupt service routine (ISR) must be part of a kernel driver and operate at a current privilege level of

0 to secure the buffer storage area.

•

Because the BTS, non-precise event-based sampling, and PEBS facilities share the same interrupt vector, the

DS ISR must check for all the possible causes of interrupts from these facilities and pass control on to the

appropriate handler.

BTS and PEBS buffer overflow would be the sources of the interrupt if the buffer index matches/exceeds the

interrupt threshold specified. Detection of non-precise event-based sampling as the source of the interrupt is

accomplished by checking for counter overflow.

•

There must be separate save areas, buffers, and state for each processor in an MP system.

•

Upon entering the ISR, branch trace messages and PEBS should be disabled to prevent race conditions during

access to the DS save area. This is done by clearing TR flag in the IA32_DEBUGCTL (or MSR_DEBUGCTLA MSR)

and by clearing the precise event enable flag in the MSR_PEBS_ENABLE MSR. These settings should be

restored to their original values when exiting the ISR.

•

The processor will not disable the DS save area when the buffer is full and the circular mode has not been

selected. The current DS setting must be retained and restored by the ISR on exit.

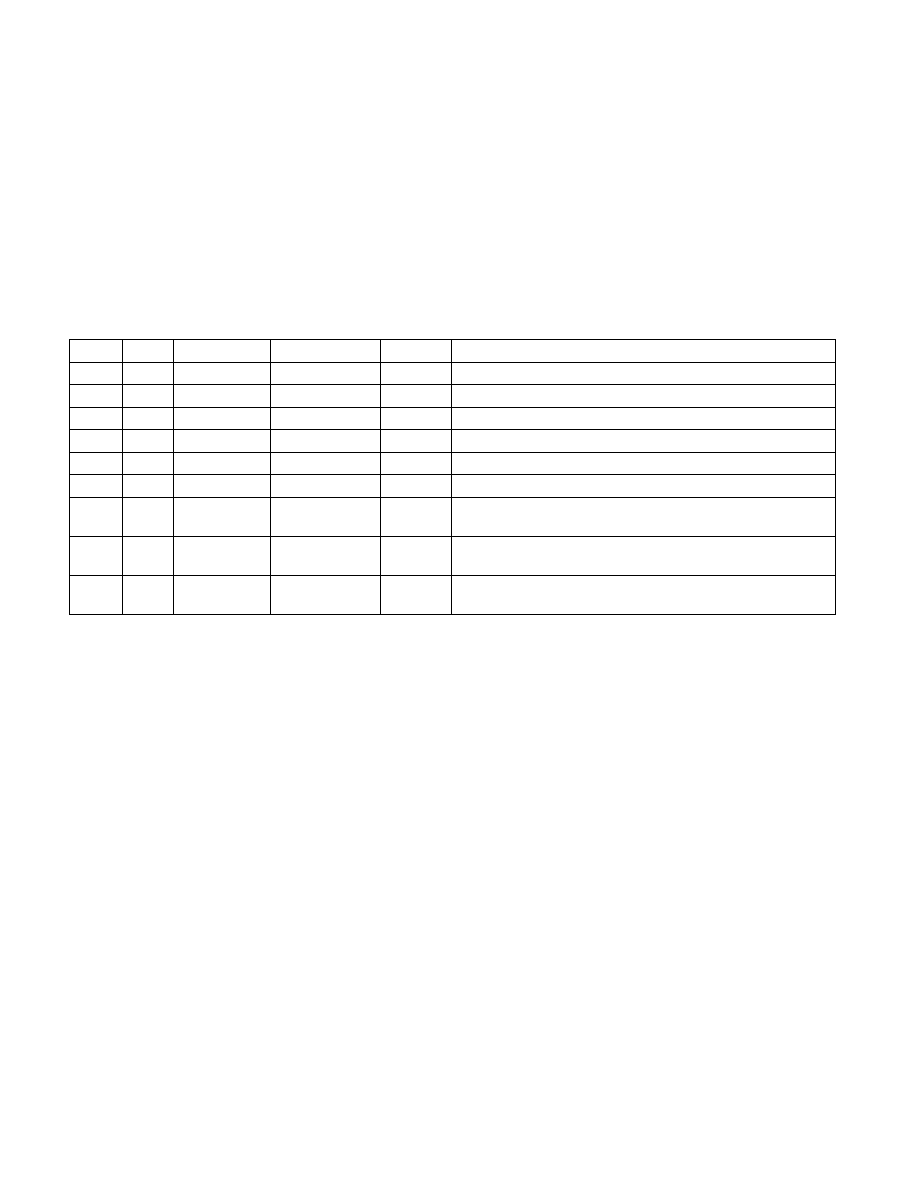

Table 17-6. CPL-Qualified Branch Trace Store Encodings

TR

BTS

BTS_OFF_OS

BTS_OFF_USR

BTINT

Description

0

X

X

X

X

Branch trace messages (BTMs) off

1

0

X

X

X

Generates BTMs but do not store BTMs

1

1

0

0

0

Store all BTMs in the BTS buffer, used here as a circular buffer

1

1

1

0

0

Store BTMs with CPL > 0 in the BTS buffer

1

1

0

1

0

Store BTMs with CPL = 0 in the BTS buffer

1

1

1

1

X

Generate BTMs but do not store BTMs

1

1

0

0

1

Store all BTMs in the BTS buffer; generate an interrupt when the

buffer is nearly full

1

1

1

0

1

Store BTMs with CPL > 0 in the BTS buffer; generate an interrupt

when the buffer is nearly full

1

1

0

1

1

Store BTMs with CPL = 0 in the BTS buffer; generate an interrupt

when the buffer is nearly full