17-20 Vol. 3B

DEBUG, BRANCH PROFILE, TSC, AND RESOURCE MONITORING FEATURES

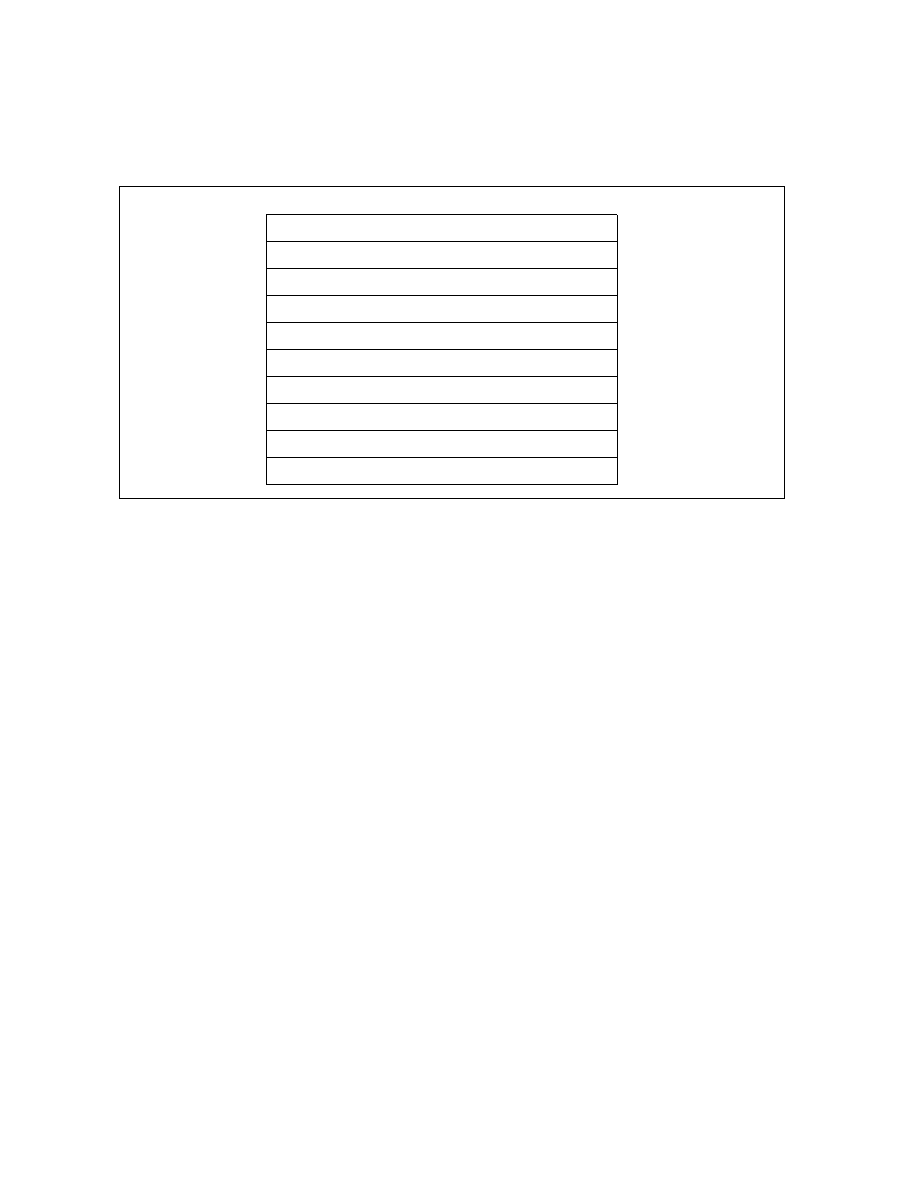

Figure 17-7 shows the structure of the 40-byte PEBS records. Nominally the register values are those at the begin-

ning of the instruction that caused the event. However, there are cases where the registers may be logged in a

partially modified state. The linear IP field shows the value in the EIP register translated from an offset into the

current code segment to a linear address.

17.4.9.1 64 Bit Format of the DS Save Area

When DTES64 = 1 (CPUID.1.ECX[2] = 1), the structure of the DS save area is shown in Figure 17-8.

When DTES64 = 0 (CPUID.1.ECX[2] = 0) and IA-32e mode is active, the structure of the DS save area is shown in

Figure 17-8. If IA-32e mode is not active the structure of the DS save area is as shown in Figure 17-6.

Figure 17-7. PEBS Record Format

EFLAGS

0H

4H

8H

0

31

Linear IP

10H

18H

14H

1CH

20H

24H

CH

EAX

EBX

ECX

EDX

ESI

EDI

EBP

ESP