Vol. 3C 35-183

MODEL-SPECIFIC REGISTERS (MSRS)

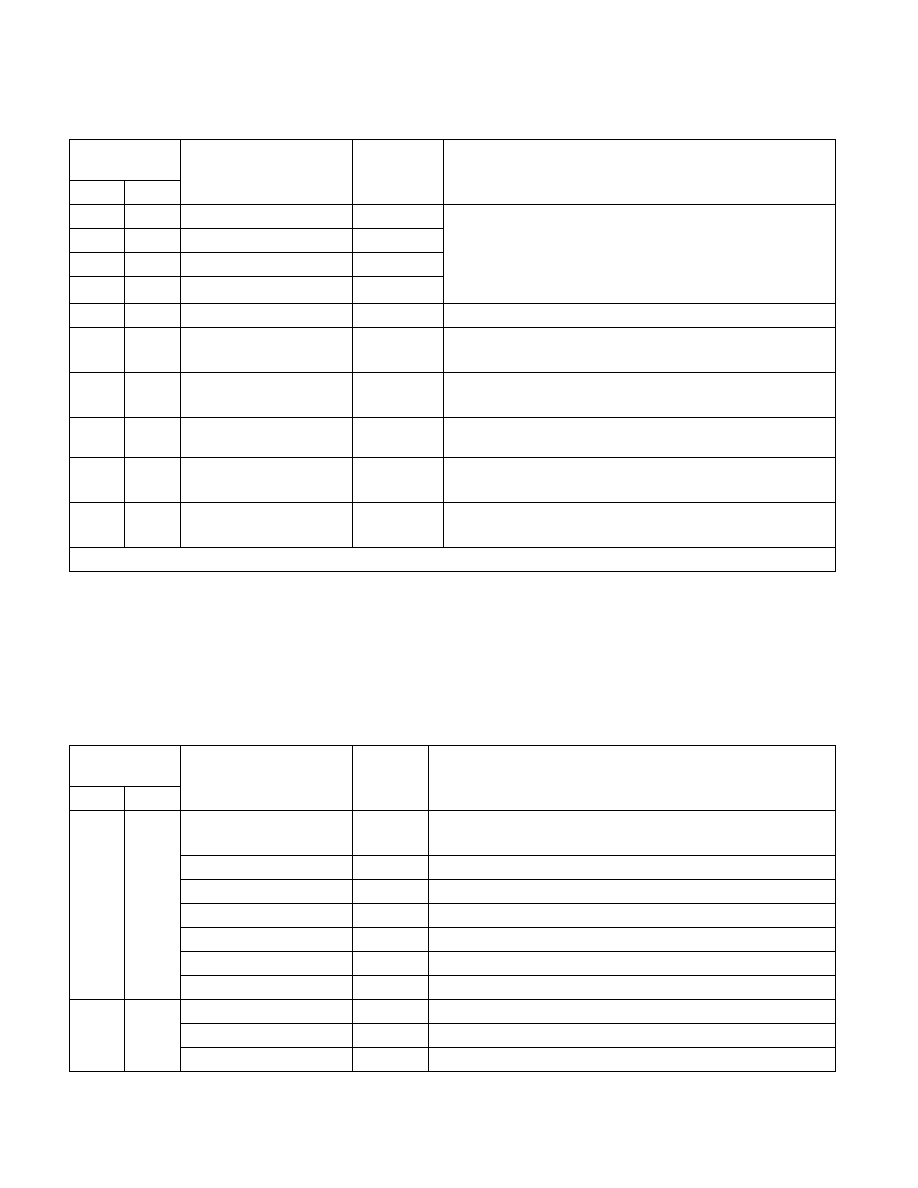

35.10.2 Additional MSRs Supported by Intel

®

Xeon

®

Processor E7 v2 Family

Intel

®

Xeon

®

processor E7 v2 family (based on Ivy Bridge-E microarchitecture) with CPUID

DisplayFamily_DisplayModel signature 06_3EH supports the MSR interfaces listed in Table 35-18, Table 35-24, and

Table 35-25.

470H

1136

IA32_MC28_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC28 reports MC error from a specific CBo (core broadcast)

and its corresponding slice of L3.

471H

1137

IA32_MC28_STATUS

Package

472H

1138

IA32_MC28_ADDR

Package

473H

1139

IA32_MC28_MISC

Package

613H

1555

MSR_PKG_PERF_STATUS

Package

Package RAPL Perf Status (R/O)

618H

1560

MSR_DRAM_POWER_LIMIT

Package

DRAM RAPL Power Limit Control (R/W)

See Section 14.9.5, “DRAM RAPL Domain.”

619H

1561

MSR_DRAM_ENERGY_

STATUS

Package

DRAM Energy Status (R/O)

See Section 14.9.5, “DRAM RAPL Domain.”

61BH

1563

MSR_DRAM_PERF_STATUS Package

DRAM Performance Throttling Status (R/O) See Section 14.9.5,

61CH

1564

MSR_DRAM_POWER_INFO

Package

DRAM RAPL Parameters (R/W)

See Section 14.9.5, “DRAM RAPL Domain.”

639H

1593

MSR_PP0_ENERGY_STATU

S

Package

PP0 Energy Status (R/O)

See Section 14.9.4, “PP0/PP1 RAPL Domains.”

See Table 35-18, for other MSR definitions applicable to Intel Xeon processor E5 v2 with CPUID signature 06_3EH

Table 35-25. Additional MSRs Supported by Intel® Xeon® Processor E7 v2 Family with DisplayFamily_DisplayModel

Signature 06_3EH

Register

Address

Register Name

Scope

Bit Description

Hex

Dec

3AH

58

IA32_FEATURE_CONTROL

Thread

Control Features in Intel 64 Processor (R/W)

See Table 35-2.

0

Lock (R/WL)

1

Enable VMX inside SMX operation (R/WL)

2

Enable VMX outside SMX operation (R/WL)

14:8

SENTER local functions enables (R/WL)

15

SENTER global functions enable (R/WL)

63:16

Reserved.

179H

377

IA32_MCG_CAP

Thread

Global Machine Check Capability (R/O)

7:0

Count

8

MCG_CTL_P

Table 35-24. MSRs Supported by Intel® Xeon® Processors E5 v2 Product Family (based on Ivy Bridge-E

microarchitecture) (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec