Vol. 3B 14-37

POWER AND THERMAL MANAGEMENT

•

Accumulated PP0 Throttled Time (bits 31:0): The unsigned integer value represents the cumulative time

(since the last time this register is cleared) that the PP0 domain has throttled. The unit of this field is specified

by the “Time Units” field of MSR_RAPL_POWER_UNIT.

14.9.5

DRAM RAPL Domain

The MSR interfaces defined for the DRAM domains are supported only in the server platform. The MSR interfaces

are:

•

MSR_DRAM_POWER_LIMIT allows software to set power limits for the DRAM domain and measurement

attributes associated with each limit.

•

MSR_DRAM_ENERGY_STATUS reports measured actual energy usage.

•

MSR_DRAM_POWER_INFO reports the DRAM domain power range information for RAPL usage.

•

MSR_DRAM_PERF_STATUS can report the performance impact of power limiting.

MSR_DRAM_POWER_LIMIT allows a software agent to define power limitation for the DRAM domain. Power limita-

tion is defined in terms of average power usage (Watts) over a time window specified in

MSR_DRAM_POWER_LIMIT. A power limit can be specified along with a time window. A lock mechanism allow the

software agent to enforce power limit settings. Once the lock bit is set, the power limit settings are static and un-

modifiable until next RESET.

The bit fields of MSR_DRAM_POWER_LIMIT (Figure 14-40) are:

•

DRAM Power Limit #1(bits 14:0): Sets the average power usage limit of the DRAM domain corresponding to

time window # 1. The unit of this field is specified by the “Power Units” field of MSR_RAPL_POWER_UNIT.

•

Enable Power Limit #1(bit 15): 0 = disabled; 1 = enabled.

•

Time Window for Power Limit (bits 23:17): Indicates the length of time window over which the power limit

will be used by the processor. The numeric value encoded by bits 23:17 is represented by the product of 2^Y

*F; where F is a single-digit decimal floating-point value between 1.0 and 1.3 with the fraction digit

represented by bits 23:22, Y is an unsigned integer represented by bits 21:17. The unit of this field is specified

by the “Time Units” field of MSR_RAPL_POWER_UNIT.

•

Lock (bit 31): If set, all write attempts to this MSR are ignored until next RESET.

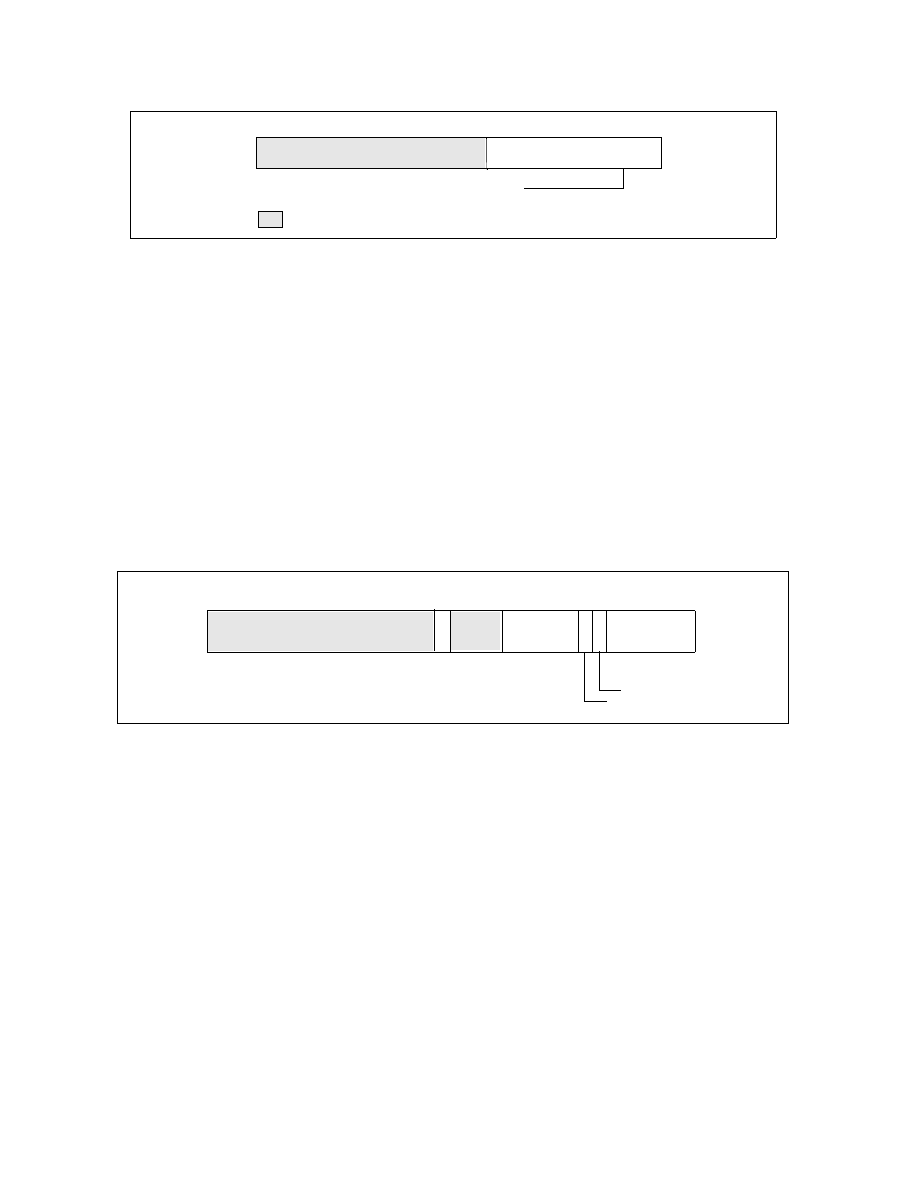

Figure 14-39. MSR_PP0_PERF_STATUS MSR

Figure 14-40. MSR_DRAM_POWER_LIMIT Register

63

0

Reserved

Accumulated PP0 throttled time

31

32

Reserved

63

Enable limit

Clamping limit

30

24 23

15

0

Power Limit

31

32

14

L

O

C

16

17

K

Time window

Power Limit