35-176 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

35.10.1 MSRs In Intel

®

Xeon

®

Processor E5 v2 Product Family (Based on Ivy Bridge-E

Microarchitecture)

Table 35-24 lists model-specific registers (MSRs) that are specific to the Intel

®

Xeon

®

Processor E5 v2 Product

Family (based on Ivy Bridge-E microarchitecture). These processors have a CPUID signature with

DisplayFamily_DisplayModel of 06_3EH, see Table 35-1. These processors supports the MSR interfaces listed in

Table 35-18, and Table 35-24.

31

TURBO_ACTIVATION_RATIO_Lock (RW/L)

When this bit is set, the content of this register is locked until a

reset.

63:32

Reserved.

See Table 35-18, Table 35-19 and Table 35-20 for other MSR definitions applicable to processors with CPUID signature

06_3AH

Table 35-24. MSRs Supported by Intel® Xeon® Processors E5 v2 Product Family (based on Ivy Bridge-E

microarchitecture)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec

4EH

78

MSR_PPIN_CTL

Package

Protected Processor Inventory Number Enable Control (R/W)

0

LockOut (R/WO)

Set 1to prevent further writes to MSR_PPIN_CTL. Writing 1 to

MSR_PPINCTL[bit 0] is permitted only if MSR_PPIN_CTL[bit 1] is

clear, Default is 0.

BIOS should provide an opt-in menu to enable the user to turn on

MSR_PPIN_CTL[bit 1] for privileged inventory initialization agent to

access MSR_PPIN. After reading MSR_PPIN, the privileged

inventory initialization agent should write ‘01b’ to MSR_PPIN_CTL

to disable further access to MSR_PPIN and prevent unauthorized

modification to MSR_PPIN_CTL.

1

Enable_PPIN (R/W)

If 1, enables MSR_PPIN to be accessible using RDMSR. Once set,

attempt to write 1 to MSR_PPIN_CTL[bit 0] will cause #GP.

If 0, an attempt to read MSR_PPIN will cause #GP. Default is 0.

63:2

Reserved.

4FH

79

MSR_PPIN

Package

Protected Processor Inventory Number (R/O)

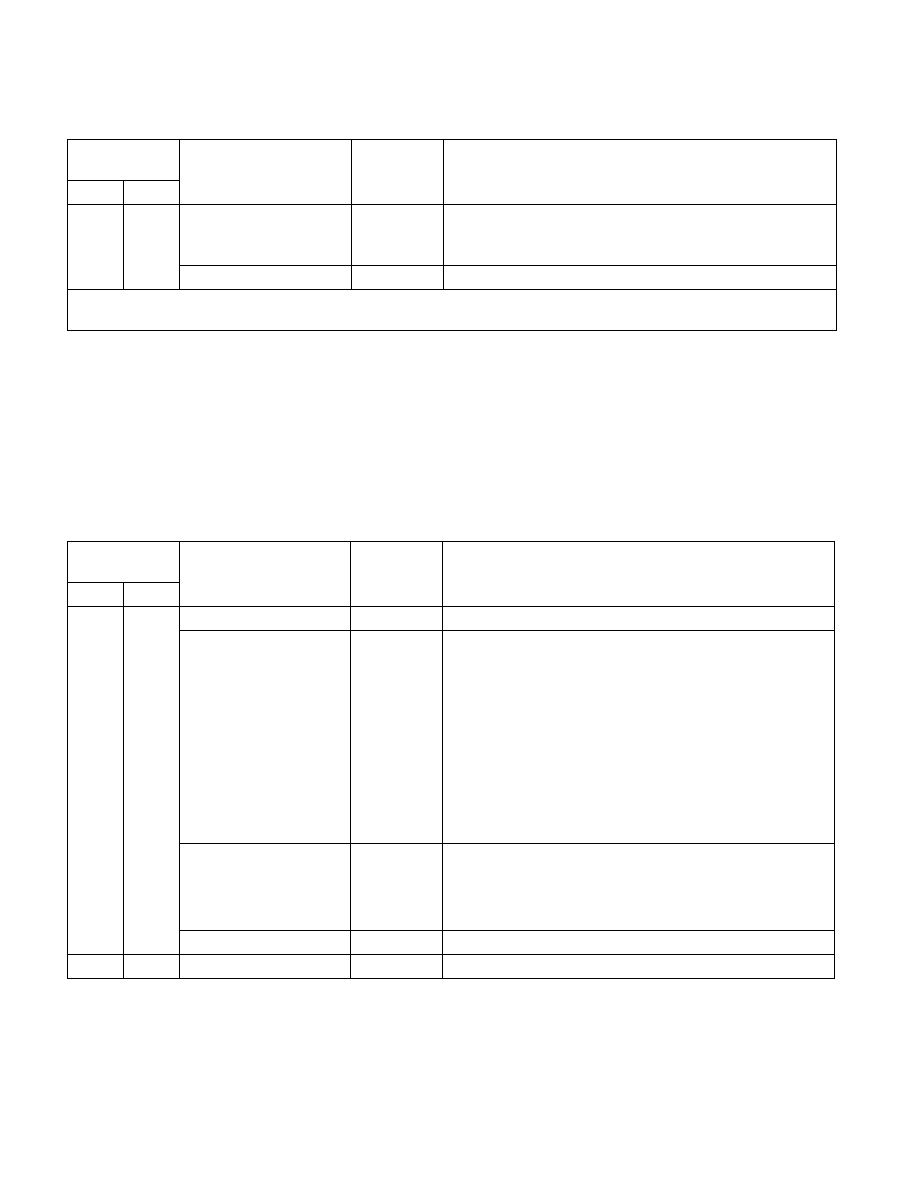

Table 35-23. Additional MSRs Supported by 3rd Generation Intel® Core™ Processors (based on Intel®

microarchitecture code name Ivy Bridge) (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec