Vol. 3C 35-169

MODEL-SPECIFIC REGISTERS (MSRS)

35.9.3 Additional Uncore PMU MSRs in the Intel

®

Xeon

®

Processor E5 Family

Intel Xeon Processor E5 family is based on the Sandy Bridge microarchitecture. The MSR-based uncore PMU inter-

faces are listed in Table 35-22. For complete detail of the uncore PMU, refer to Intel Xeon Processor E5 Product

Family Uncore Performance Monitoring Guide. These processors have a CPUID signature with

DisplayFamily_DisplayModel of 06_2DH

443H

1091

IA32_MC16_MISC

Package

See Section 15.3.2.4, “IA32_MCi_MISC MSRs.”

444H

1092

IA32_MC17_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.”

445H

1093

IA32_MC17_STATUS

Package

See Section 15.3.2.2, “IA32_MCi_STATUS MSRS,” and Chapter 16.

446H

1094

IA32_MC17_ADDR

Package

See Section 15.3.2.3, “IA32_MCi_ADDR MSRs.”

447H

1095

IA32_MC17_MISC

Package

See Section 15.3.2.4, “IA32_MCi_MISC MSRs.”

448H

1096

IA32_MC18_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.”

449H

1097

IA32_MC18_STATUS

Package

See Section 15.3.2.2, “IA32_MCi_STATUS MSRS,” and Chapter 16.

44AH

1098

IA32_MC18_ADDR

Package

See Section 15.3.2.3, “IA32_MCi_ADDR MSRs.”

44BH

1099

IA32_MC18_MISC

Package

See Section 15.3.2.4, “IA32_MCi_MISC MSRs.”

44CH

1100

IA32_MC19_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.”

44DH

1101

IA32_MC19_STATUS

Package

See Section 15.3.2.2, “IA32_MCi_STATUS MSRS,” and Chapter 16.

44EH

1102

IA32_MC19_ADDR

Package

See Section 15.3.2.3, “IA32_MCi_ADDR MSRs.”

44FH

1103

IA32_MC19_MISC

Package

See Section 15.3.2.4, “IA32_MCi_MISC MSRs.”

613H

1555

MSR_PKG_PERF_STATUS

Package

Package RAPL Perf Status (R/O)

618H

1560

MSR_DRAM_POWER_LIMIT

Package

DRAM RAPL Power Limit Control (R/W)

See Section 14.9.5, “DRAM RAPL Domain.”

619H

1561

MSR_DRAM_ENERGY_

STATUS

Package

DRAM Energy Status (R/O)

See Section 14.9.5, “DRAM RAPL Domain.”

61BH

1563

MSR_DRAM_PERF_STATUS Package

DRAM Performance Throttling Status (R/O) See Section 14.9.5,

61CH

1564

MSR_DRAM_POWER_INFO

Package

DRAM RAPL Parameters (R/W)

See Section 14.9.5, “DRAM RAPL Domain.”

639H

1593

MSR_PP0_ENERGY_STATU

S

Package

PP0 Energy Status (R/O)

See Section 14.9.4, “PP0/PP1 RAPL Domains.”

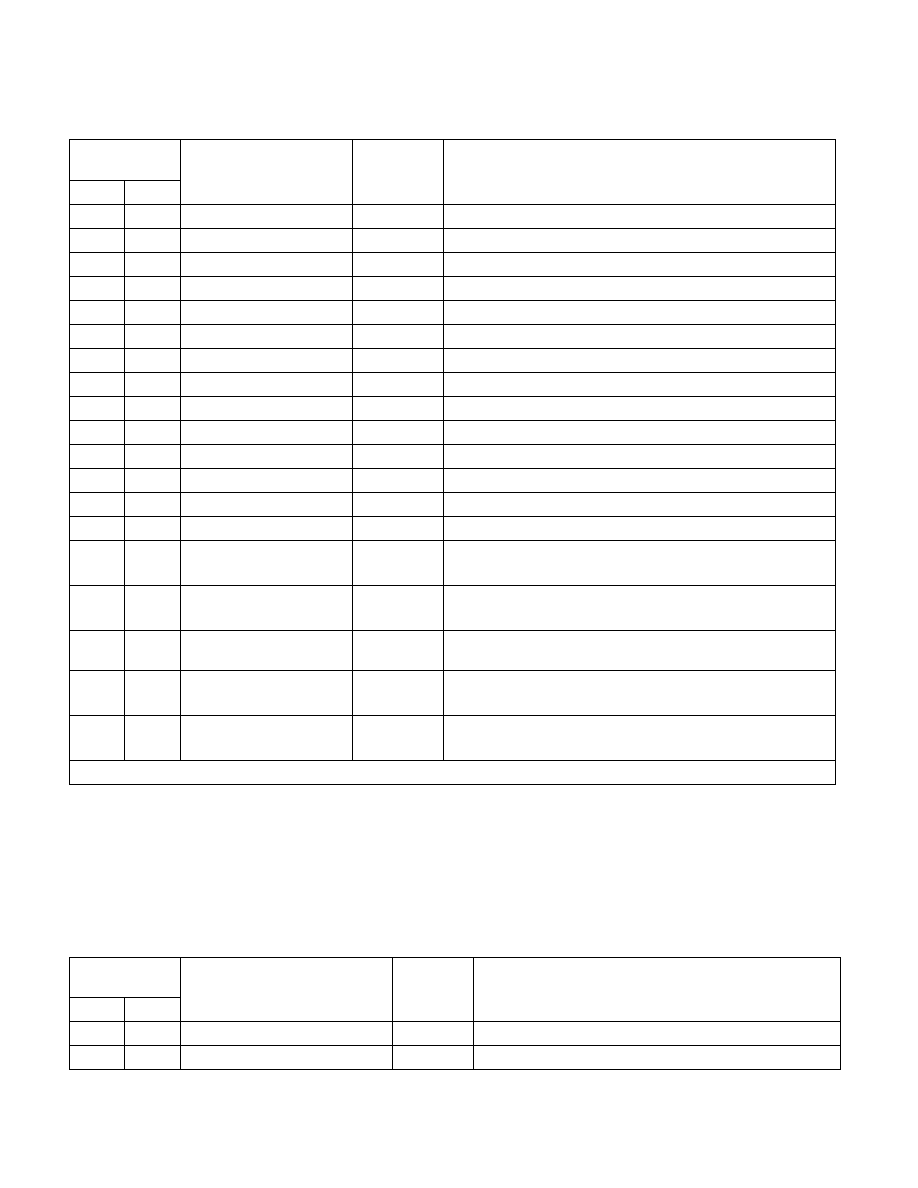

See Table 35-18, Table 35-21, and Table 35-22 for MSR definitions applicable to processors with CPUID signature 06_2DH.

Table 35-22. Uncore PMU MSRs in Intel® Xeon® Processor E5 Family

Register

Address

Register Name

Scope

Bit Description

Hex

Dec

C08H

MSR_U_PMON_UCLK_FIXED_CTL

Package

Uncore U-box UCLK fixed counter control

C09H

MSR_U_PMON_UCLK_FIXED_CTR

Package

Uncore U-box UCLK fixed counter

Table 35-21. Selected MSRs Supported by Intel® Xeon® Processors E5 Family (based on Sandy Bridge

microarchitecture) (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec