35-166 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

35.9.2 MSRs In Intel

®

Xeon

®

Processor E5 Family (Based on Intel

®

Microarchitecture Code

Name Sandy Bridge)

Table 35-21 lists additional model-specific registers (MSRs) that are specific to the Intel

®

Xeon

®

Processor E5

Family (based on Intel

®

microarchitecture code name Sandy Bridge). These processors have a CPUID signature

with DisplayFamily_DisplayModel of 06_2DH, and also supports MSRs listed in Table 35-18 and Table 35-22.

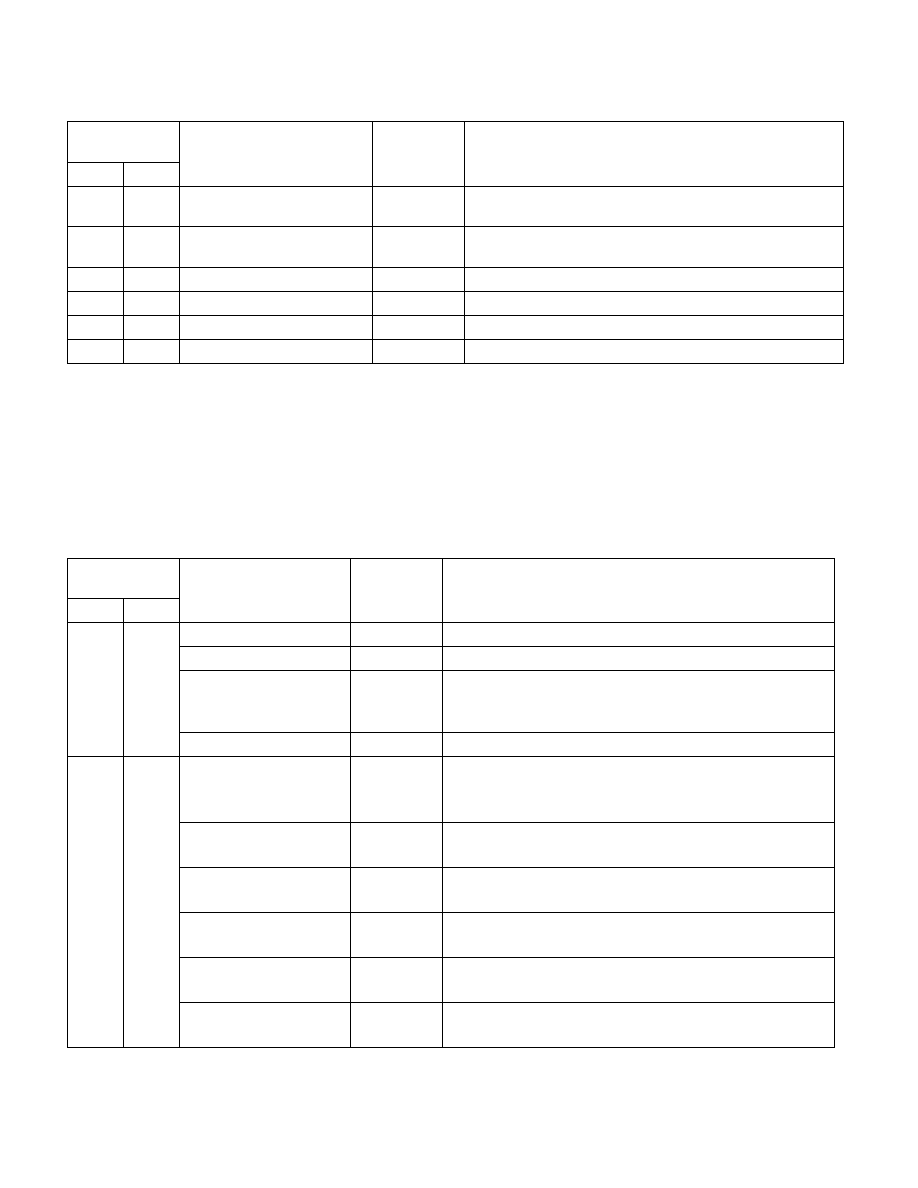

743H

1859

MSR_UNC_CBO_4_

PERFEVTSEL3

Package

Uncore C-Box 4, counter 3 event select MSR.

745H

1861

MSR_UNC_CBO_4_UNIT_

STATUS

Package

Uncore C-Box 4, unit status for counter 0-3

746H

1862

MSR_UNC_CBO_4_PERFCTR0

Package

Uncore C-Box 4, performance counter 0.

747H

1863

MSR_UNC_CBO_4_PERFCTR1

Package

Uncore C-Box 4, performance counter 1.

748H

1864

MSR_UNC_CBO_4_PERFCTR2

Package

Uncore C-Box 4, performance counter 2.

749H

1865

MSR_UNC_CBO_4_PERFCTR3

Package

Uncore C-Box 4, performance counter 3.

Table 35-21. Selected MSRs Supported by Intel® Xeon® Processors E5 Family (based on Sandy Bridge

microarchitecture)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec

17FH

383

MSR_ERROR_CONTROL

Package

MC Bank Error Configuration (R/W)

0

Reserved

1

MemError Log Enable (R/W)

When set, enables IMC status bank to log additional info in bits

36:32.

63:2

Reserved.

1ADH

429

MSR_TURBO_RATIO_LIMIT

Package

Maximum Ratio Limit of Turbo Mode

RO if MSR_PLATFORM_INFO.[28] = 0,

RW if MSR_PLATFORM_INFO.[28] = 1

7:0

Package

Maximum Ratio Limit for 1C

Maximum turbo ratio limit of 1 core active.

15:8

Package

Maximum Ratio Limit for 2C

Maximum turbo ratio limit of 2 core active.

23:16

Package

Maximum Ratio Limit for 3C

Maximum turbo ratio limit of 3 core active.

31:24

Package

Maximum Ratio Limit for 4C

Maximum turbo ratio limit of 4 core active.

39:32

Package

Maximum Ratio Limit for 5C

Maximum turbo ratio limit of 5 core active.

Table 35-20. Uncore PMU MSRs Supported by 2nd Generation Intel® Core™ Processors

Register

Address

Register Name

Scope

Bit Description

Hex

Dec