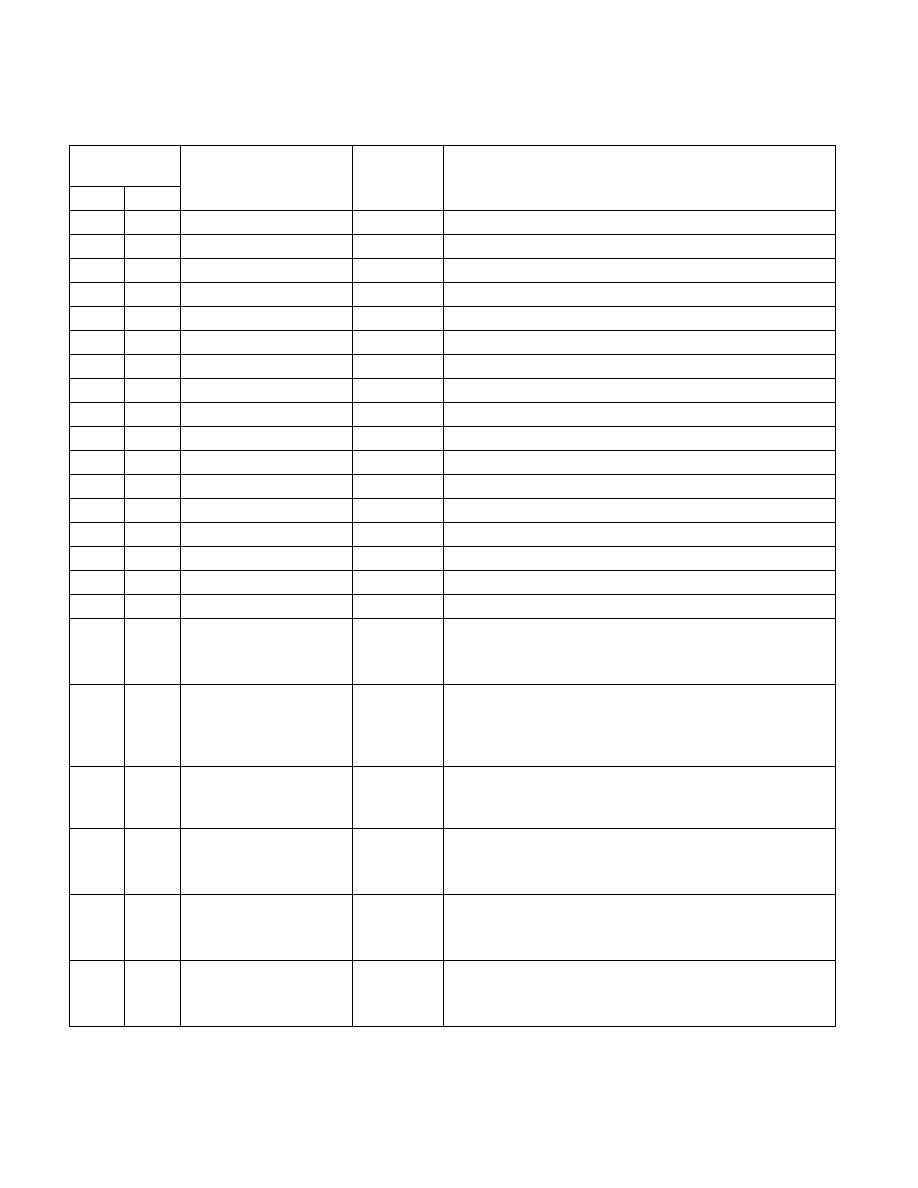

Vol. 3C 35-119

MODEL-SPECIFIC REGISTERS (MSRS)

413H

1043

IA32_MC4_MISC

Core

See Section 15.3.2.4, “IA32_MCi_MISC MSRs.”

414H

1044

IA32_MC5_CTL

Core

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.”

415H

1045

IA32_MC5_STATUS

Core

See Section 15.3.2.2, “IA32_MCi_STATUS MSRS.”

416H

1046

IA32_MC5_ADDR

Core

See Section 15.3.2.3, “IA32_MCi_ADDR MSRs.”

417H

1047

IA32_MC5_MISC

Core

See Section 15.3.2.4, “IA32_MCi_MISC MSRs.”

418H

1048

IA32_MC6_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.”

419H

1049

IA32_MC6_STATUS

Package

See Section 15.3.2.2, “IA32_MCi_STATUS MSRS,” and Chapter 16.

41AH

1050

IA32_MC6_ADDR

Package

See Section 15.3.2.3, “IA32_MCi_ADDR MSRs.”

41BH

1051

IA32_MC6_MISC

Package

See Section 15.3.2.4, “IA32_MCi_MISC MSRs.”

41CH

1052

IA32_MC7_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.”

41DH

1053

IA32_MC7_STATUS

Package

See Section 15.3.2.2, “IA32_MCi_STATUS MSRS,” and Chapter 16.

41EH

1054

IA32_MC7_ADDR

Package

See Section 15.3.2.3, “IA32_MCi_ADDR MSRs.”

41FH

1055

IA32_MC7_MISC

Package

See Section 15.3.2.4, “IA32_MCi_MISC MSRs.”

420H

1056

IA32_MC8_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.”

421H

1057

IA32_MC8_STATUS

Package

See Section 15.3.2.2, “IA32_MCi_STATUS MSRS,” and Chapter 16.

422H

1058

IA32_MC8_ADDR

Package

See Section 15.3.2.3, “IA32_MCi_ADDR MSRs.”

423H

1059

IA32_MC8_MISC

Package

See Section 15.3.2.4, “IA32_MCi_MISC MSRs.”

480H

1152

IA32_VMX_BASIC

Thread

Reporting Register of Basic VMX Capabilities (R/O)

See Table 35-2.

See Appendix A.1, “Basic VMX Information.”

481H

1153

IA32_VMX_PINBASED_

CTLS

Thread

Capability Reporting Register of Pin-based VM-execution

Controls (R/O)

See Table 35-2.

See Appendix A.3, “VM-Execution Controls.”

482H

1154

IA32_VMX_PROCBASED_

CTLS

Thread

Capability Reporting Register of Primary Processor-based

VM-execution Controls (R/O)

See Appendix A.3, “VM-Execution Controls.”

483H

1155

IA32_VMX_EXIT_CTLS

Thread

Capability Reporting Register of VM-exit Controls (R/O)

See Table 35-2.

See Appendix A.4, “VM-Exit Controls.”

484H

1156

IA32_VMX_ENTRY_CTLS

Thread

Capability Reporting Register of VM-entry Controls (R/O)

See Table 35-2.

See Appendix A.5, “VM-Entry Controls.”

485H

1157

IA32_VMX_MISC

Thread

Reporting Register of Miscellaneous VMX Capabilities (R/O)

See Table 35-2.

See Appendix A.6, “Miscellaneous Data.”

Table 35-13. MSRs in Processors Based on Intel® Microarchitecture Code Name Nehalem (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec