Vol. 3B 18-65

PERFORMANCE MONITORING

18.11.1 Processor Event Based Sampling (PEBS) Facility

The PEBS facility in the 4th Generation Intel Core processor is similar to those in processors based on Intel micro-

architecture code name Sandy Bridge, with several enhanced features. The key components and differences of

PEBS facility relative to Intel microarchitecture code name Sandy Bridge is summarized in Table 18-43.

Only IA32_PMC0 through IA32_PMC3 support PEBS.

NOTE

PEBS events are only valid when the following fields of IA32_PERFEVTSELx are all zero: AnyThread,

Edge, Invert, CMask.

In a PMU with PDIR capability, PEBS behavior is unpredictable if IA32_PERFEVTSELx or IA32_PMCx

is changed for a PEBS-enabled counter while an event is being counted. To avoid this, changes to

the programming or value of a PEBS-enabled counter should be performed when the counter is

disabled.

18.11.2 PEBS Data Format

The PEBS record format for the 4th Generation Intel Core processor is shown in Table 18-44. The PEBS record

format, along with debug/store area storage format, does not change regardless of whether IA-32e mode is active

or not. CPUID.01H:ECX.DTES64[bit 2] reports whether the processor's DS storage format support is mode-inde-

pendent. When set, it uses 64-bit DS storage format.

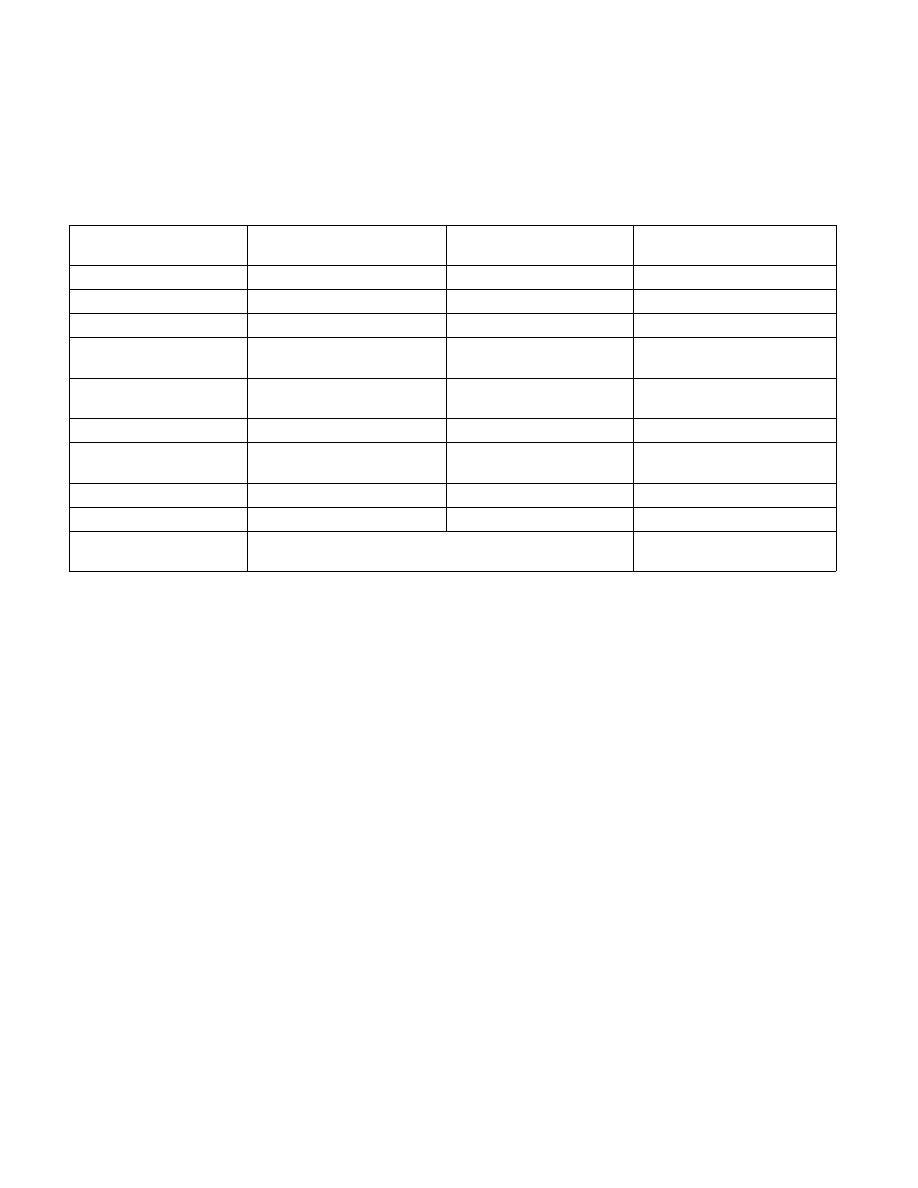

Table 18-43. PEBS Facility Comparison

Box

Intel® microarchitecture code

name Haswell

Intel® microarchitecture code

name Sandy Bridge

Comment

Valid IA32_PMCx

PMC0-PMC3

PMC0-PMC3

No PEBS on PMC4-PMC7

PEBS Buffer Programming

Unchanged

IA32_PEBS_ENABLE Layout

PEBS record layout

Table 18-44; enhanced fields at

offsets 98H, A0H, A8H, B0H.

Table 18-23; enhanced fields

at offsets 98H, A0H, A8H.

Precise Events

See Table 18-32.

IA32_PMC4-IA32_PMC7 do not

support PEBS.

PEBS-Load Latency

See Table 18-33.

PEBS-Precise Store

No, replaced by data address

profiling.

Yes; see Section 18.9.4.3.

PEBS-PDIR

Yes

Yes

IA32_PMC1 only.

PEBS skid from EventingIP

1 (or 2 if micro+macro fusion)

1

SAMPLING Restriction

Small SAV(CountDown) value incur higher overhead than prior

generation.