18-66 Vol. 3B

PERFORMANCE MONITORING

The layout of PEBS records are almost identical to those shown in Table 18-23. Offset B0H is a new field that

records the eventing IP address of the retired instruction that triggered the PEBS assist.

The PEBS records at offsets 98H, A0H, and ABH record data gathered from three of the PEBS capabilities in prior

processor generations: load latency facility (Section 18.9.4.2), PDIR (Section 18.9.4.4), and the equivalent capa-

bility of precise store in prior generation (see Section 18.11.3).

In the core PMU of the 4th generation Intel Core processor, load latency facility and PDIR capabilities are

unchanged. However, precise store is replaced by an enhanced capability, data address profiling, that is not

restricted to store address. Data address profiling also records information in PEBS records at offsets 98H, A0H,

and ABH.

18.11.3 PEBS Data Address Profiling

The Data Linear Address facility is also abbreviated as DataLA. The facility is a replacement or extension of the

precise store facility in previous processor generations. The DataLA facility complements the load latency facility by

providing a means to profile load and store memory references in the system, leverages the PEBS facility, and

provides additional information about sampled loads and stores. Having precise memory reference events with

linear address information for both loads and stores provides information to improve data structure layout, elimi-

nate remote node references, and identify cache-line conflicts in NUMA systems.

The DataLA facility in the 4th generation processor supports the following events configured to use PEBS:

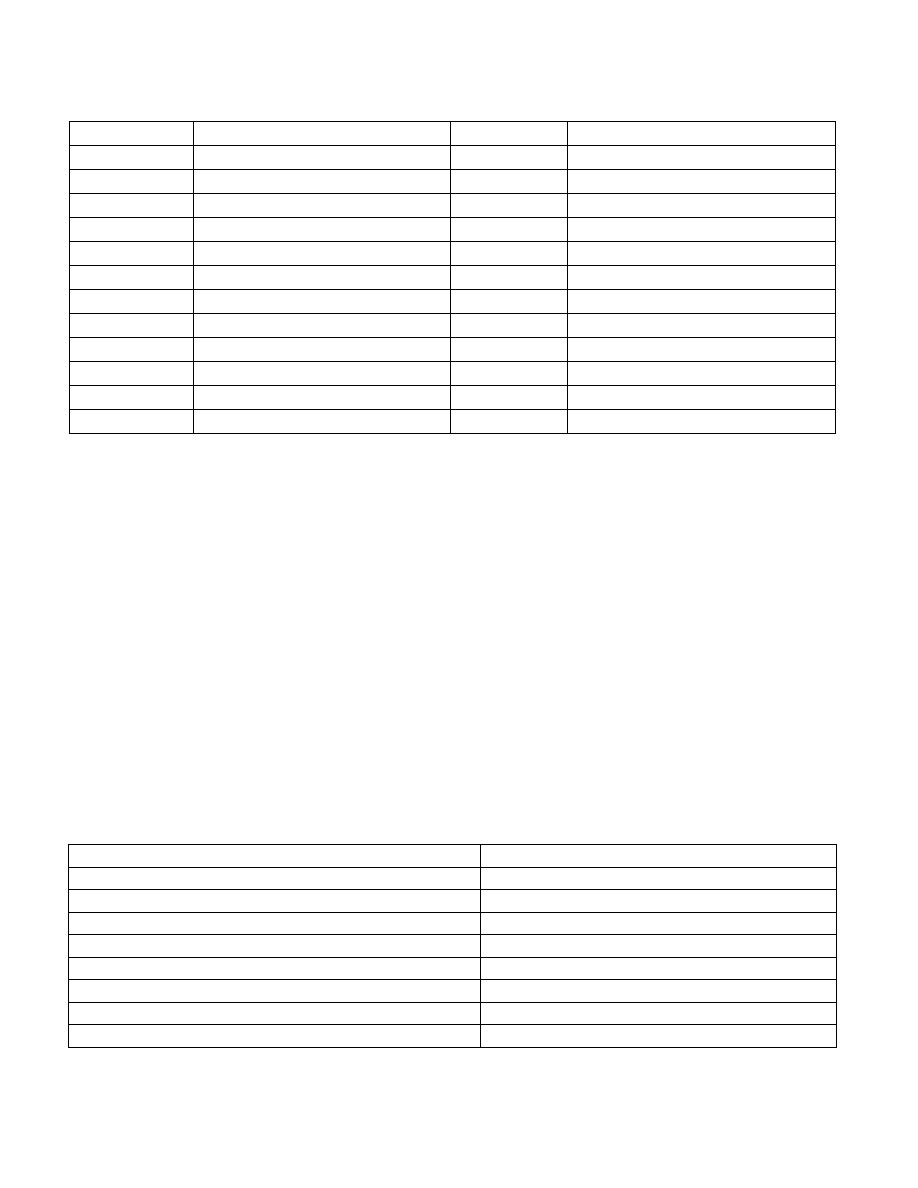

Table 18-44. PEBS Record Format for 4th Generation Intel Core Processor Family

Byte Offset

Field

Byte Offset

Field

00H

R/EFLAGS

60H

R10

08H

R/EIP

68H

R11

10H

R/EAX

70H

R12

18H

R/EBX

78H

R13

20H

R/ECX

80H

R14

28H

R/EDX

88H

R15

30H

R/ESI

90H

IA32_PERF_GLOBAL_STATUS

38H

R/EDI

98H

Data Linear Address

40H

R/EBP

A0H

Data Source Encoding

48H

R/ESP

A8H

Latency value (core cycles)

50H

R8

B0H

EventingIP

58H

R9

B8H

TX Abort Information (Section 18.11.5.1)

Table 18-45. Precise Events That Supports Data Linear Address Profiling

Event Name

Event Name

MEM_UOPS_RETIRED.STLB_MISS_LOADS

MEM_UOPS_RETIRED.STLB_MISS_STORES

MEM_UOPS_RETIRED.LOCK_LOADS

MEM_UOPS_RETIRED.SPLIT_STORES

MEM_UOPS_RETIRED.SPLIT_LOADS

MEM_UOPS_RETIRED.ALL_STORES

MEM_UOPS_RETIRED.ALL_LOADS

MEM_LOAD_UOPS_LLC_MISS_RETIRED.LOCAL_DRAM

MEM_LOAD_UOPS_RETIRED.L1_HIT

MEM_LOAD_UOPS_RETIRED.L2_HIT

MEM_LOAD_UOPS_RETIRED.L3_HIT

MEM_LOAD_UOPS_RETIRED.L1_MISS

MEM_LOAD_UOPS_RETIRED.L2_MISS

MEM_LOAD_UOPS_RETIRED.L3_MISS

MEM_LOAD_UOPS_RETIRED.HIT_LFB

MEM_LOAD_UOPS_L3_HIT_RETIRED.XSNP_MISS