18-50 Vol. 3B

PERFORMANCE MONITORING

Details of the uncore performance monitoring facility of Intel Xeon Processor E7 family is available in the “Intel®

Xeon® Processor E7 Uncore Performance Monitoring Programming Reference Manual”.

18.9

PERFORMANCE MONITORING FOR PROCESSORS BASED ON INTEL

®

MICROARCHITECTURE CODE NAME SANDY BRIDGE

Intel

®

Core™ i7-2xxx, Intel

®

Core™ i5-2xxx, Intel

®

Core™ i3-2xxx processor series, and Intel

®

Xeon

®

processor

E3-1200 family are based on Intel microarchitecture code name Sandy Bridge; this section describes the perfor-

mance monitoring facilities provided in the processor core. The core PMU supports architectural performance moni-

toring capability with version ID 3 (see Section 18.2.3) and a host of non-architectural monitoring capabilities.

Architectural performance monitoring version 3 capabilities are described in Section 18.2.3.

The core PMU’s capability is similar to those described in Section 18.8.1 and Section 18.8.4, with some differences

and enhancements relative to Intel microarchitecture code name Westmere summarized in Table 18-30.

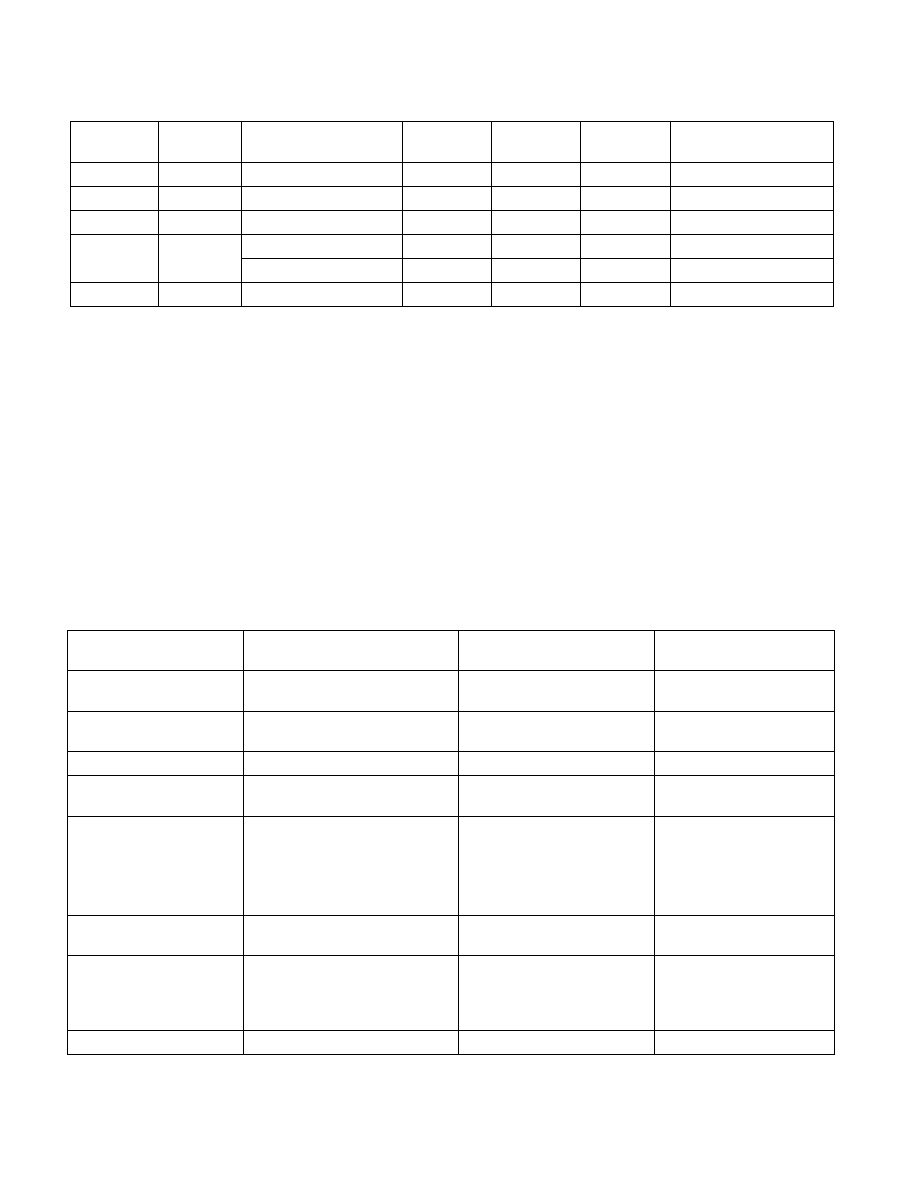

B-Box

2

4

48

Yes

per-box

Match/Mask

M-Box

2

6

48

Yes

per-box

Yes

R-Box

1

16 ( 2 port, 8 per port)

48

Yes

per-box

Yes

W-Box

1

4

48

Yes

per-box

None

1

48

No

per-box

None

U-Box

1

1

48

Yes

uncore

None

Table 18-30. Core PMU Comparison

Box

Intel® microarchitecture code

name Sandy Bridge

Intel® microarchitecture code

name Westmere

Comment

# of Fixed counters per

thread

3

3

Use CPUID to enumerate # of

counters.

# of general-purpose

counters per core

8

8

Counter width (R,W)

R:48, W: 32/48

R:48, W:32

See Section 18.2.2.

# of programmable counters

per thread

4 or (8 if a core not shared by two

threads)

4

Use CPUID to enumerate # of

counters.

PMI Overhead Mitigation

• Freeze_Perfmon_on_PMI with

legacy semantics.

• Freeze_on_LBR with legacy

semantics for branch profiling.

• Freeze_while_SMM.

• Freeze_Perfmon_on_PMI

with legacy semantics.

• Freeze_on_LBR with legacy

semantics for branch

profiling.

• Freeze_while_SMM.

See Section 17.4.7.

Processor Event Based

Sampling (PEBS) Events

IA32_PMC4-IA32_PMC7 do

not support PEBS.

PEBS-Load Latency

See Section 18.9.4.2;

• Data source encoding

• STLB miss encoding

• Lock transaction encoding

Data source encoding

PEBS-Precise Store

No

Table 18-29. Uncore PMU MSR Summary for Intel® Xeon® Processor E7 Family

Box

# of Boxes

Counters per Box

Counter

Width

General

Purpose

Global

Enable Sub-control

MSRs