Vol. 3B 18-49

PERFORMANCE MONITORING

The individual MSRs that provide uncore PMU interfaces are listed in Chapter 35, Table 35-15 under the general

naming style of MSR_%box#%_PMON_%scope_function%, where %box#% designates the type of box and zero-

based index if there are more the one box of the same type, %scope_function% follows the examples below:

ÔÇó

Multi-counter enabling MSRs: MSR_U_PMON_GLOBAL_CTL, MSR_S0_PMON_BOX_CTL,

MSR_C7_PMON_BOX_CTL, etc.

ÔÇó

Multi-counter status MSRs: MSR_U_PMON_GLOBAL_STATUS, MSR_S0_PMON_BOX_STATUS,

MSR_C7_PMON_BOX_STATUS, etc.

ÔÇó

Multi-counter overflow control MSRs: MSR_U_PMON_GLOBAL_OVF_CTL, MSR_S0_PMON_BOX_OVF_CTL,

MSR_C7_PMON_BOX_OVF_CTL, etc.

ÔÇó

Performance counters MSRs: the scope is implicitly per counter, e.g. MSR_U_PMON_CTR,

MSR_S0_PMON_CTR0, MSR_C7_PMON_CTR5, etc.

ÔÇó

Event select MSRs: the scope is implicitly per counter, e.g. MSR_U_PMON_EVNT_SEL,

MSR_S0_PMON_EVNT_SEL0, MSR_C7_PMON_EVNT_SEL5, etc

ÔÇó

Sub-control MSRs: the scope is implicitly per-box granularity, e.g.

MSR_M0_PMON_TIMESTAMP,

MSR_R0_PMON_IPERF0_P1, MSR_S1_PMON_MATCH.

Details of uncore PMU MSR bit field definitions can be found in a separate document ÔÇťIntel Xeon Processor 7500

Series Uncore Performance Monitoring GuideÔÇť.

18.8.4

Performance Monitoring for Processors Based on Intel

®

Microarchitecture Code Name

Westmere

All of the performance monitoring programming interfaces (architectural and non-architectural core PMU facilities,

and uncore PMU) described in Section 18.8 also apply to processors based on Intel

®

microarchitecture code name

Westmere.

Table 18-25 describes a non-architectural performance monitoring event (event code 0B7H) and associated

MSR_OFFCORE_RSP_0 (address 1A6H) in the core PMU. This event and a second functionally equivalent offcore

response event using event code 0BBH and MSR_OFFCORE_RSP_1 (address 1A7H) are supported in processors

based on Intel microarchitecture code name Westmere. The event code and event mask definitions of Non-archi-

tectural performance monitoring events are listed in Table 19-26.

The load latency facility is the same as described in Section 18.8.1.2, but added enhancement to provide more

information in the data source encoding field of each load latency record. The additional information relates to

STLB_MISS and LOCK, see Table 18-33.

18.8.5 Intel

®

Xeon

®

Processor E7 Family Performance Monitoring Facility

The performance monitoring facility in the processor core of the Intel

®

Xeon

®

processor E7 family is the same as

those supported in the Intel Xeon processor 5600 series

3

. The uncore subsystem in the Intel Xeon processor E7

family is similar to those of the Intel Xeon processor 7500 series. The high level construction of the uncore sub-

system is similar to that shown in Figure 18-31, with the additional capability that up to 10 C-Box units are

supported.

Table 18-29 summarizes the number MSRs for uncore PMU for each box.

3. Exceptions are indicated for event code 0FH in Table 19-19; and valid bits of data source encoding field of each load

latency record is

limited to bits 5:4 of Table 18-33.

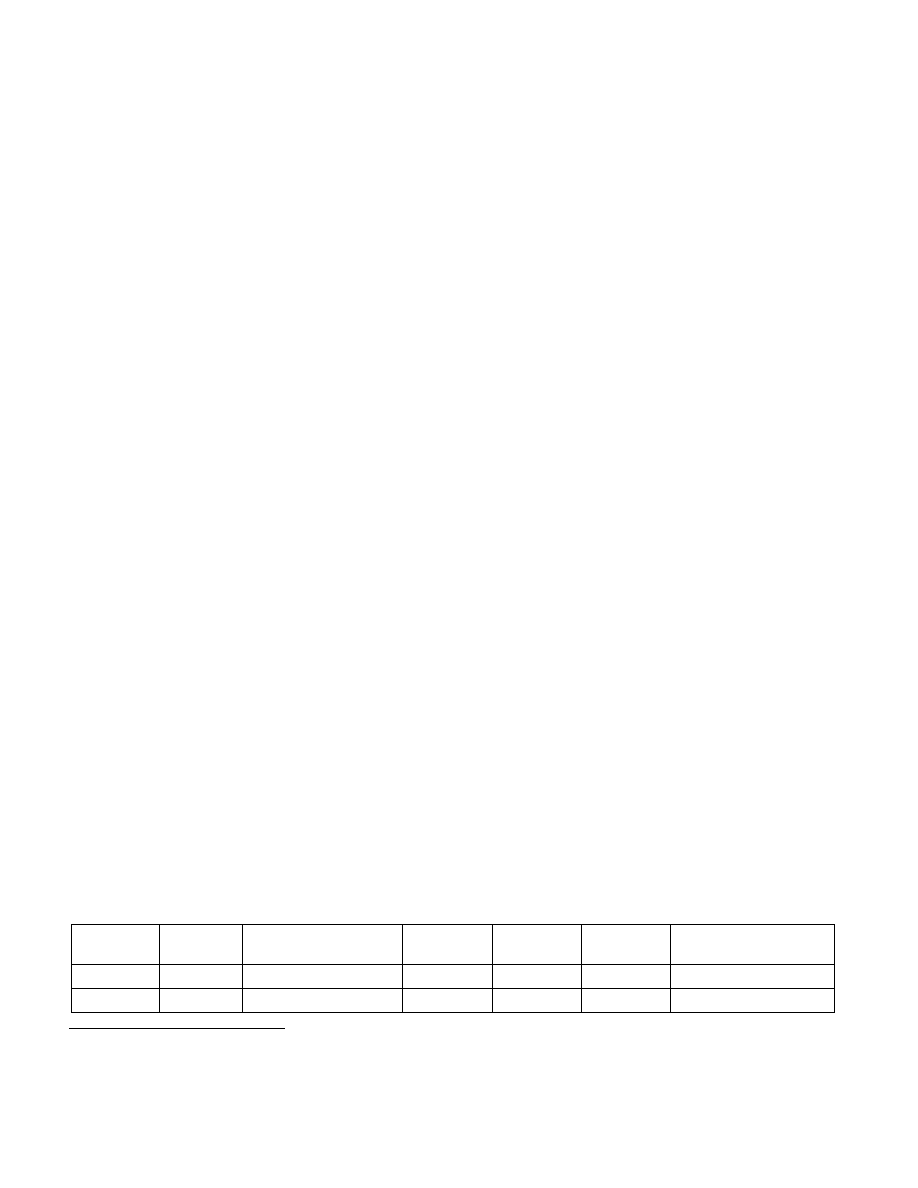

Table 18-29. Uncore PMU MSR Summary for Intel® Xeon® Processor E7 Family

Box

# of Boxes

Counters per Box

Counter

Width

General

Purpose

Global

Enable Sub-control

MSRs

C-Box

10

6

48

Yes

per-box

None

S-Box

2

4

48

Yes

per-box

Match/Mask