18-8 Vol. 3B

PERFORMANCE MONITORING

When a performance counter is configured for PEBS, overflow condition in the counter generates a performance-

monitoring interrupt signaling a PEBS event. On a PEBS event, the processor stores data records into the buffer

area (see Section 18.15.5), clears the counter overflow status., and sets the “OvfBuffer” bit in

IA32_PERF_GLOBAL_STATUS.

IA32_PERF_GLOBAL_OVF_CTL MSR allows software to clear overflow indicator(s) of any general-purpose or fixed-

function counters via a single WRMSR. Software should clear overflow indications when

•

Setting up new values in the event select and/or UMASK field for counting or interrupt-based event sampling.

•

Reloading counter values to continue collecting next sample.

•

Disabling event counting or interrupt-based event sampling.

The layout of IA32_PERF_GLOBAL_OVF_CTL is shown in Figure 18-5.

18.2.3

Architectural Performance Monitoring Version 3

Processors supporting architectural performance monitoring version 3 also supports version 1 and 2, as well as

capability enumerated by CPUID leaf 0AH. Specifically, version 3 provides the following enhancement in perfor-

mance monitoring facilities if a processor core comprising of more than one logical processor, i.e. a processor core

supporting Intel Hyper-Threading Technology or simultaneous multi-threading capability:

•

Anythread counting for processor core supporting two or more logical processors. The interface that supports

AnyThread counting include:

— Each IA32_PERFEVTSELx MSR (starting at MSR address 186H) support the bit field layout defined in Figure

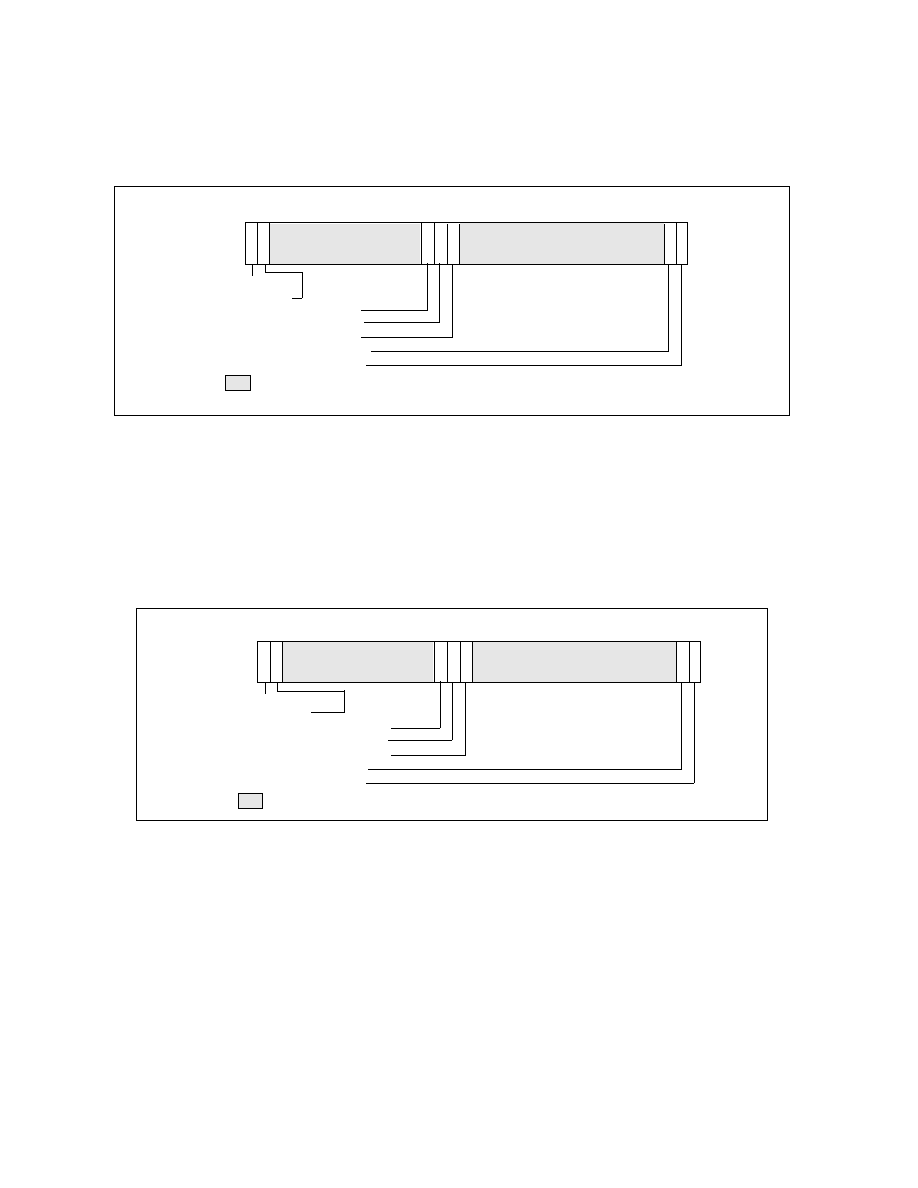

Figure 18-4. Layout of IA32_PERF_GLOBAL_STATUS MSR

Figure 18-5. Layout of IA32_PERF_GLOBAL_OVF_CTRL MSR

62

IA32_FIXED_CTR2 Overflow

IA32_FIXED_CTR1 Overflow

IA32_FIXED_CTR0 Overflow

IA32_PMC1 Overflow

2 1 0

IA32_PMC0 Overflow

31

32

33

34

35

Reserved

63

CondChgd

OvfDSBuffer

62

IA32_FIXED_CTR2 ClrOverflow

IA32_FIXED_CTR1 ClrOverflow

IA32_FIXED_CTR0 ClrOverflow

IA32_PMC1 ClrOverflow

2 1 0

IA32_PMC0 ClrOverflow

31

32

33

34

35

Reserved

63

ClrCondChgd

ClrOvfDSBuffer