Vol. 3B 18-41

PERFORMANCE MONITORING

18.8.1.3 Off-core Response Performance Monitoring in the Processor Core

Programming a performance event using the off-core response facility can choose any of the four

IA32_PERFEVTSELx MSR with specific event codes and predefine mask bit value. Each event code for off-core

response monitoring requires programming an associated configuration MSR, MSR_OFFCORE_RSP_0. There is

only one off-core response configuration MSR. Table 18-25 lists the event code, mask value and additional off-core

configuration MSR that must be programmed to count off-core response events using IA32_PMCx.

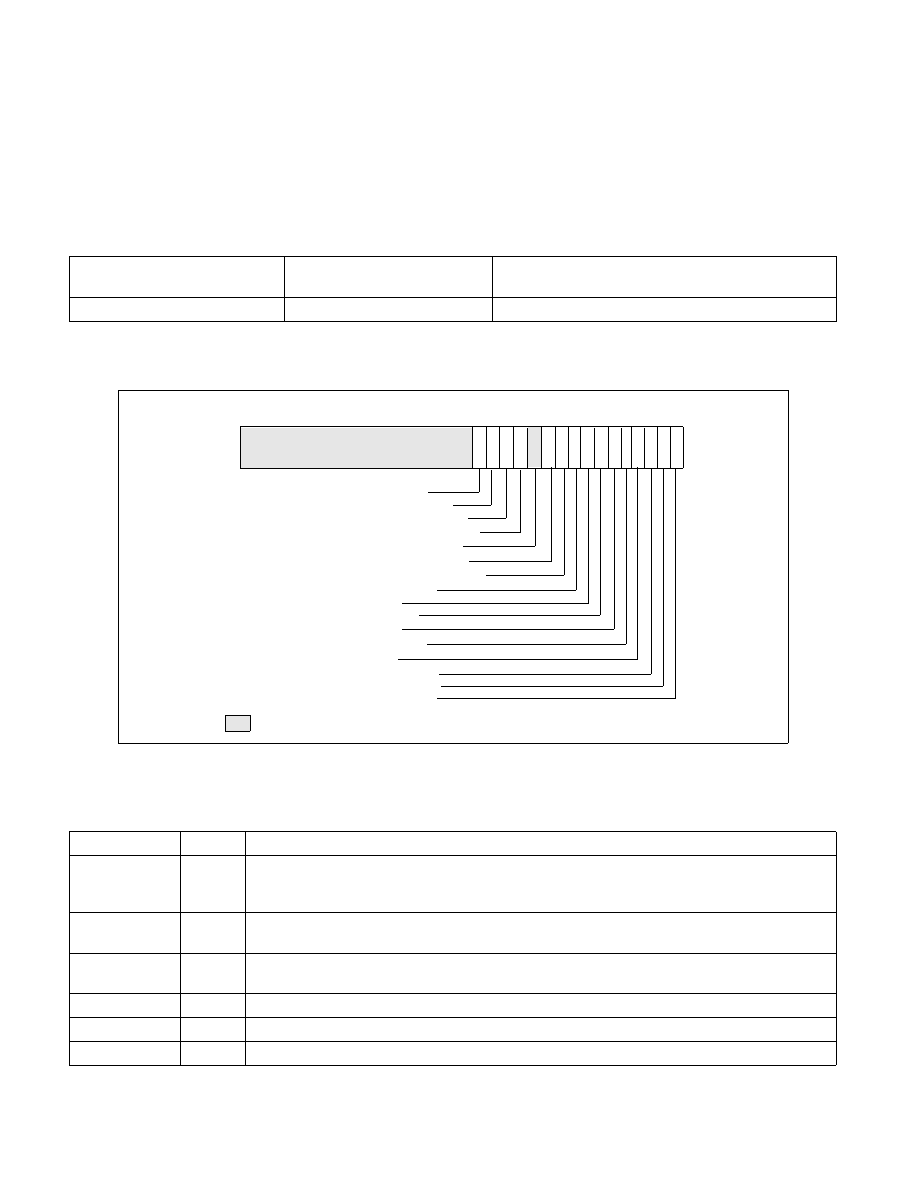

The layout of MSR_OFFCORE_RSP_0 is shown in Figure 18-24. Bits 7:0 specifies the request type of a transaction

request to the uncore. Bits 15:8 specifies the response of the uncore subsystem.

Table 18-25. Off-Core Response Event Encoding

Event code in

IA32_PERFEVTSELx

Mask Value in

IA32_PERFEVTSELx

Required Off-core Response MSR

B7H

01H

MSR_OFFCORE_RSP_0 (address 1A6H)

Figure 18-24. Layout of MSR_OFFCORE_RSP_0 and MSR_OFFCORE_RSP_1 to Configure Off-core Response Events

Table 18-26. MSR_OFFCORE_RSP_0 and MSR_OFFCORE_RSP_1 Bit Field Definition

Bit Name

Offset

Description

DMND_DATA_RD 0

(R/W). Counts the number of demand and DCU prefetch data reads of full and partial cachelines as well

as demand data page table entry cacheline reads. Does not count L2 data read prefetches or

instruction fetches.

DMND_RFO

1

(R/W). Counts the number of demand and DCU prefetch reads for ownership (RFO) requests generated

by a write to data cacheline. Does not count L2 RFO.

DMND_IFETCH

2

(R/W). Counts the number of demand and DCU prefetch instruction cacheline reads. Does not count L2

code read prefetches.

WB

3

(R/W). Counts the number of writeback (modified to exclusive) transactions.

PF_DATA_RD

4

(R/W). Counts the number of data cacheline reads generated by L2 prefetchers.

PF_RFO

5

(R/W). Counts the number of RFO requests generated by L2 prefetchers.

RESPONSE TYPE — NON_DRAM (R/W)

RESPONSE TYPE — LOCAL_DRAM (R/W)

RESPONSE TYPE — REMOTE_DRAM (R/W)

RESPONSE TYPE — REMOTE_CACHE_FWD (R/W)

8 7

0

RESPONSE TYPE — RESERVED

11

3

12

1

Reserved

63

2

4

9

5

6

10

13

14

15

RESPONSE TYPE — OTHER_CORE_HITM (R/W)

RESPONSE TYPE — OTHER_CORE_HIT_SNP (R/W)

RESPONSE TYPE — UNCORE_HIT (R/W)

REQUEST TYPE — OTHER (R/W)

REQUEST TYPE — PF_IFETCH (R/W)

REQUEST TYPE — PF_RFO (R/W)

REQUEST TYPE — PF_DATA_RD (R/W)

REQUEST TYPE — WB (R/W)

REQUEST TYPE — DMND_IFETCH (R/W)

REQUEST TYPE — DMND_RFO (R/W)

REQUEST TYPE — DMND_DATA_RD (R/W)

RESET Value — 00000000_00000000H