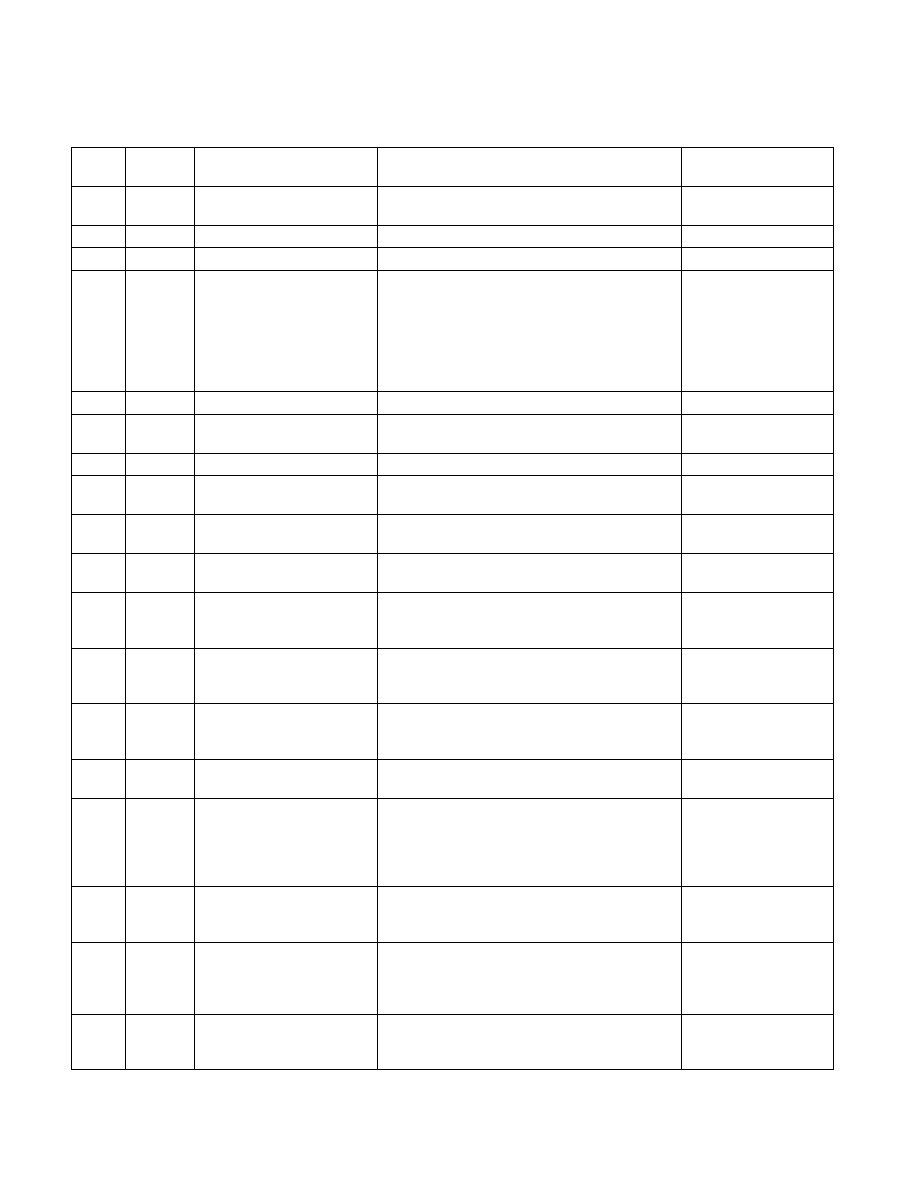

19-86 Vol. 3B

PERFORMANCE-MONITORING EVENTS

Table 19-19. Non-Architectural Performance Events In the Processor Core for

Processors Based on Intel® Microarchitecture Code Name Westmere

Event

Num.

Umask

Value

Event Mask Mnemonic

Description

Comment

03H

02H

LOAD_BLOCK.OVERLAP_STOR

E

Loads that partially overlap an earlier store.

04H

07H

SB_DRAIN.ANY

All Store buffer stall cycles.

05H

02H

MISALIGN_MEMORY.STORE

All store referenced with misaligned address.

06H

04H

STORE_BLOCKS.AT_RET

Counts number of loads delayed with at-Retirement

block code. The following loads need to be executed

at retirement and wait for all senior stores on the

same thread to be drained: load splitting across 4K

boundary (page split), load accessing uncacheable

(UC or WC) memory, load lock, and load with page

table in UC or WC memory region.

06H

08H

STORE_BLOCKS.L1D_BLOCK

Cacheable loads delayed with L1D block code.

07H

01H

PARTIAL_ADDRESS_ALIAS

Counts false dependency due to partial address

aliasing.

08H

01H

DTLB_LOAD_MISSES.ANY

Counts all load misses that cause a page walk.

08H

02H

DTLB_LOAD_MISSES.WALK_C

OMPLETED

Counts number of completed page walks due to load

miss in the STLB.

08H

04H

DTLB_LOAD_MISSES.WALK_CY

CLES

Cycles PMH is busy with a page walk due to a load

miss in the STLB.

08H

10H

DTLB_LOAD_MISSES.STLB_HI

T

Number of cache load STLB hits.

08H

20H

DTLB_LOAD_MISSES.PDE_MIS

S

Number of DTLB cache load misses where the low

part of the linear to physical address translation

was missed.

0BH

01H

MEM_INST_RETIRED.LOADS

Counts the number of instructions with an

architecturally-visible load retired on the

architected path.

0BH

02H

MEM_INST_RETIRED.STORES

Counts the number of instructions with an

architecturally-visible store retired on the

architected path.

0BH

10H

MEM_INST_RETIRED.LATENCY

_ABOVE_THRESHOLD

Counts the number of instructions exceeding the

latency specified with ld_lat facility.

In conjunction with ld_lat

facility.

0CH

01H

MEM_STORE_RETIRED.DTLB_

MISS

The event counts the number of retired stores that

missed the DTLB. The DTLB miss is not counted if

the store operation causes a fault. Does not counter

prefetches. Counts both primary and secondary

misses to the TLB.

0EH

01H

UOPS_ISSUED.ANY

Counts the number of Uops issued by the Register

Allocation Table to the Reservation Station, i.e. the

UOPs issued from the front end to the back end.

0EH

01H

UOPS_ISSUED.STALLED_CYCL

ES

Counts the number of cycles no uops issued by the

Register Allocation Table to the Reservation

Station, i.e. the UOPs issued from the front end to

the back end.

Set “invert=1, cmask =

1“.

0EH

02H

UOPS_ISSUED.FUSED

Counts the number of fused Uops that were issued

from the Register Allocation Table to the

Reservation Station.