18-48 Vol. 3B

PERFORMANCE MONITORING

Table 18-28 summarizes the number MSRs for uncore PMU for each box.

The W-Box provides 4 general-purpose counters, each requiring an event select configuration MSR, similar to the

general-purpose counters in other boxes. There is also a fixed-function counter that increments clockticks in the

uncore clock domain.

For C,S,B,M,R, and W boxes, each box provides an MSR to enable/disable counting, configuring PMI of multiple

counters within the same box, this is somewhat similar the “global control“ programming interface,

IA32_PERF_GLOBAL_CTRL, offered in the core PMU. Similarly status information and counter overflow control for

multiple counters within the same box are also provided in C,S,B,M,R, and W boxes.

In the U-Box, MSR_U_PMON_GLOBAL_CTL provides overall uncore PMU enable/disable and PMI configuration

control. The scope of status information in the U-box is at per-box granularity, in contrast to the per-box status

information MSR (in the C,S,B,M,R, and W boxes) providing status information of individual counter overflow. The

difference in scope also apply to the overflow control MSR in the U-Box versus those in the other Boxes.

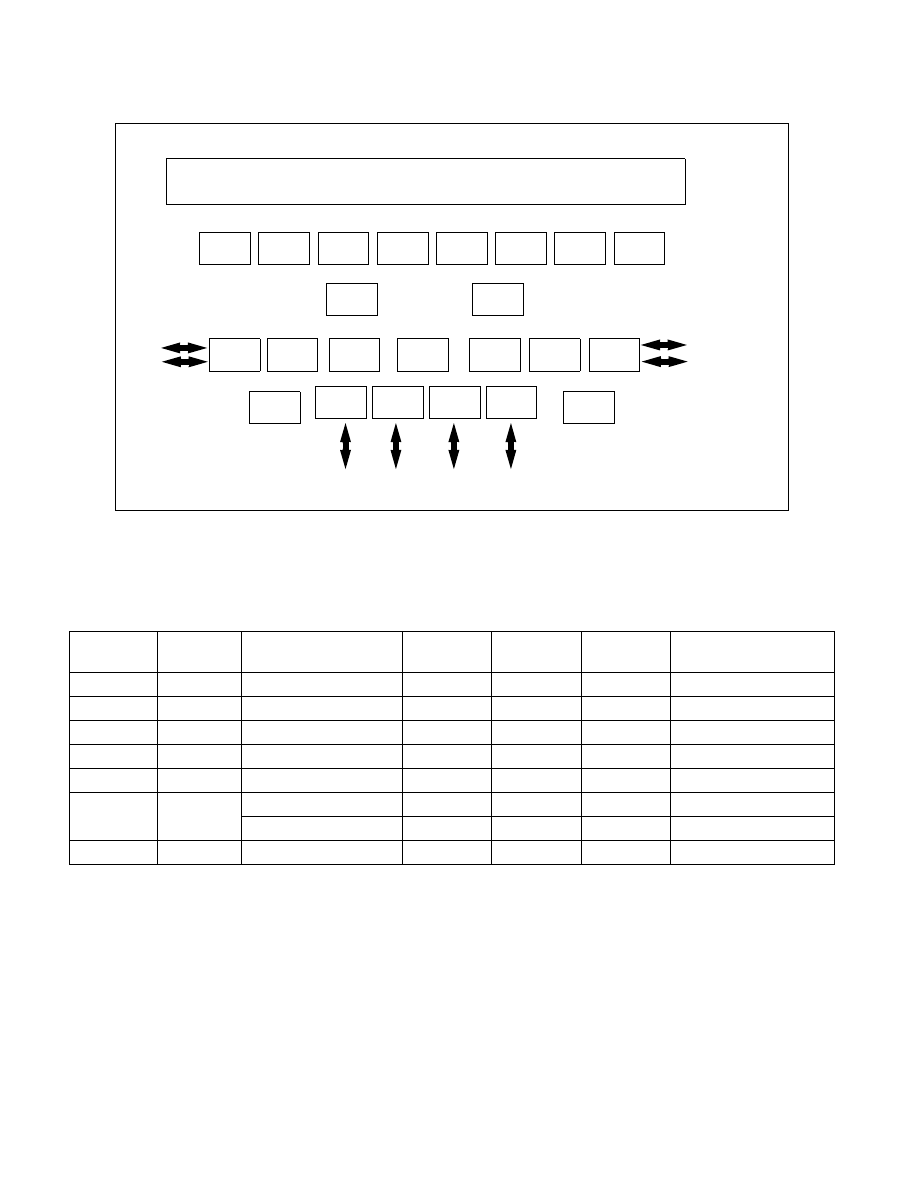

Figure 18-31. Distributed Units of the Uncore of Intel® Xeon® Processor 7500 Series

Table 18-28. Uncore PMU MSR Summary

Box

# of Boxes

Counters per Box

Counter

Width

General

Purpose

Global

Enable Sub-control

MSRs

C-Box

8

6

48

Yes

per-box

None

S-Box

2

4

48

Yes

per-box

Match/Mask

B-Box

2

4

48

Yes

per-box

Match/Mask

M-Box

2

6

48

Yes

per-box

Yes

R-Box

1

16 ( 2 port, 8 per port)

48

Yes

per-box

Yes

W-Box

1

4

48

Yes

per-box

None

1

48

No

per-box

None

U-Box

1

1

48

Yes

uncore

None

PBox

L3 Cache

PBox

PBox

PBox

UBox

WBox

RBox

BBox

BBox

MBox

MBox

PBox

PBox

SBox

SBox

CBox

CBox

CBox

CBox

CBox

CBox

CBox

CBox

4 Intel QPI Links

SMI Channels

SMI Channels