Vol. 3B 18-29

PERFORMANCE MONITORING

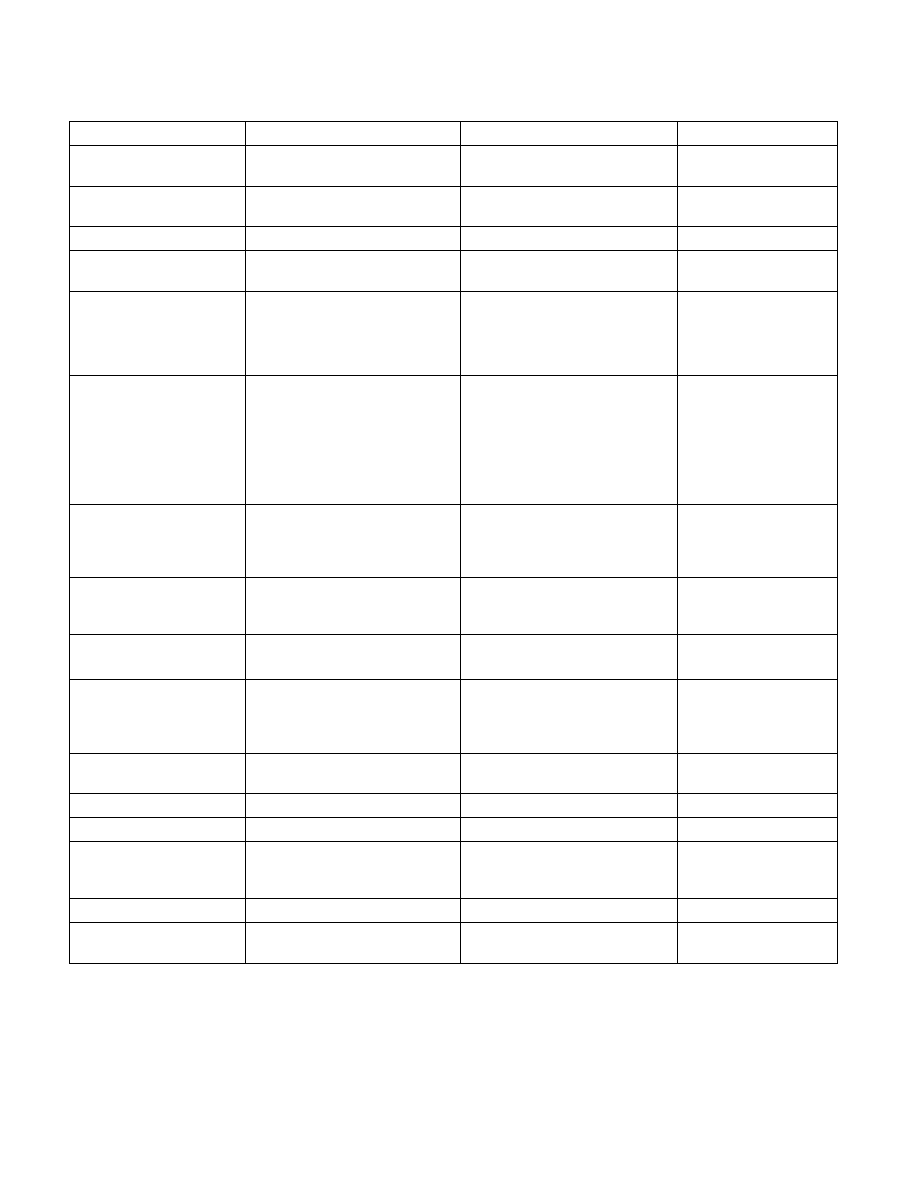

Table 18-18. Core PMU Comparison Between the Goldmont and Silvermont Microarchitectures

Box

The Goldmont microarchitecture

The Silvermont microarchitecture Comment

# of Fixed counters per core 3

3

Use CPUID to enumerate

# of counters.

# of general-purpose

counters per core

4

2

Counter width (R,W)

R:48, W: 32/48

R:40, W:32

Architectural Performance

Monitoring version ID

4

3

Use CPUID to enumerate

# of counters.

PMI Overhead Mitigation

• Freeze_Perfmon_on_PMI with

streamlined semantics.

• Freeze_on_LBR with legacy

semantics for branch profiling.

• Freeze_while_SMM.

• Freeze_Perfmon_on_PMI with

legacy semantics.

• Freeze_on_LBR with legacy

semantics for branch profiling.

• Freeze_while_SMM.

See Section 17.4.7.

Legacy semantics not

supported with version 4

or higher.

Counter and Buffer

Overflow Status

Management

• Query via

IA32_PERF_GLOBAL_STATUS

• Reset via

IA32_PERF_GLOBAL_STATUS_R

ESET

• Set via

IA32_PERF_GLOBAL_STATUS_S

ET

• Query via

IA32_PERF_GLOBAL_STATUS

• Reset via

IA32_PERF_GLOBAL_OVF_CTRL

IA32_PERF_GLOBAL_STATU

S Indicators of

Overflow/Overhead/Interfer

ence

• Individual counter overflow

• PEBS buffer overflow

• ToPA buffer overflow

• CTR_Frz, LBR_Frz

• Individual counter overflow

• PEBS buffer overflow

Enable control in

IA32_PERF_GLOBAL_STATU

S

• CTR_Frz,

• LBR_Frz

No

Perfmon Counter In-Use

Indicator

Query IA32_PERF_GLOBAL_INUSE

No

Processor Event Based

Sampling (PEBS) Events

General-Purpose Counter 0 only.

Supports all events (precise and

non-precise). Precise events are

listed in Table 18-19.

See Section 18.6.1.1. General-

Purpose Counter 0 only. Only

supports precise events (see

IA32_PMC0 only.

PEBS record format

encoding

0011b

0010b

Reduce skid PEBS

IA32_PMC0 only

No

Data Address Profiling

Yes

No

PEBS record layout

Table 18-20; enhanced fields at

offsets 90H- 98H; and TSC record

field at C0H.

PEBS EventingIP

Yes

Yes

Off-core Response Event

MSR 1A6H and 1A7H, each core

has its own register.

MSR 1A6H and 1A7H, shared by a

pair of cores.

Nehalem supports 1A6H

only.