18-30 Vol. 3B

PERFORMANCE MONITORING

18.7.1

Processor Event Based Sampling (PEBS)

Processor event based sampling (PEBS) on the Goldmont microarchitecture is enhanced over prior generations

with respect to sampling support of precise events and non-precise events. In the Goldmont microarchitecture,

PEBS is supported using IA32_PMC0 for all events (see Section 17.4.9).

PEBS uses a debug store mechanism to store a set of architectural state information for the processor at the time

the sample was generated.

Precise events work the same way as on the Silvermont microarchitecture. They can capture precise eventingIP asso-

ciated with a retired instruction that caused the event.

The PEBS record provides architectural state of the instruc-

tion executed after the instruction that caused the event (See Section 18.4.4 and Section 17.4.9). The PEBS record

also provides architectural state of the processor after the instruction that caused the event completes. The list of

precise events supported in the Goldmont microarchitecture is shown in Table 18-19.

In the Goldmont microarchitecture, the PEBS facility also supports the use of non-precise events to record

processor state information into PEBS records with the same format as with precise events.

However, a non-precise event may not be attributable to a particular retired instruction or the time of instruction

execution. When the counter overflows, a PEBS record will be generated at the next opportunity. Consider the

event ICACHE.HIT. When the counter overflows, the processor is fetching future instructions. The PEBS record will

be generated at the next opportunity and capture the state at the processor's current retirement point. Other

examples of a non-precise events are CPU_CLK_UNHALTED.CORE_P and HARDWARE_INTERRUPTS.RECEIVED.

There may be many instructions in various stages of execution, multiple or zero instructions being retired each

cycle as CPU_CLK_UNHALTED.CORE_P increments. HARDWARE_INTERRUPTS.RECEIVED increments independent

of any instructions being executed. The PEBS record will be generated at the next opportunity, capturing the

processor state when the machine received the interrupt, even if interrupts are masked. The PEBS facility thus

allows for identification of the instructions which were executing when the event overflowed.

After generating a record, the PEBS facility reloads the counter and resumes execution, just as is done for precise

events. Unlike interrupt-based sampling, which requires an interrupt service routine to collect the sample and

reload the counter, the PEBS facility can collect samples even when interrupts are masked

and without using NMI

.

Since a PEBS record is generated immediately when a counter for a non-precise event is enabled, it may also be

generated after an overflow is set by an MSR write to IA32_PERF_GLOBAL_STATUS_SET.

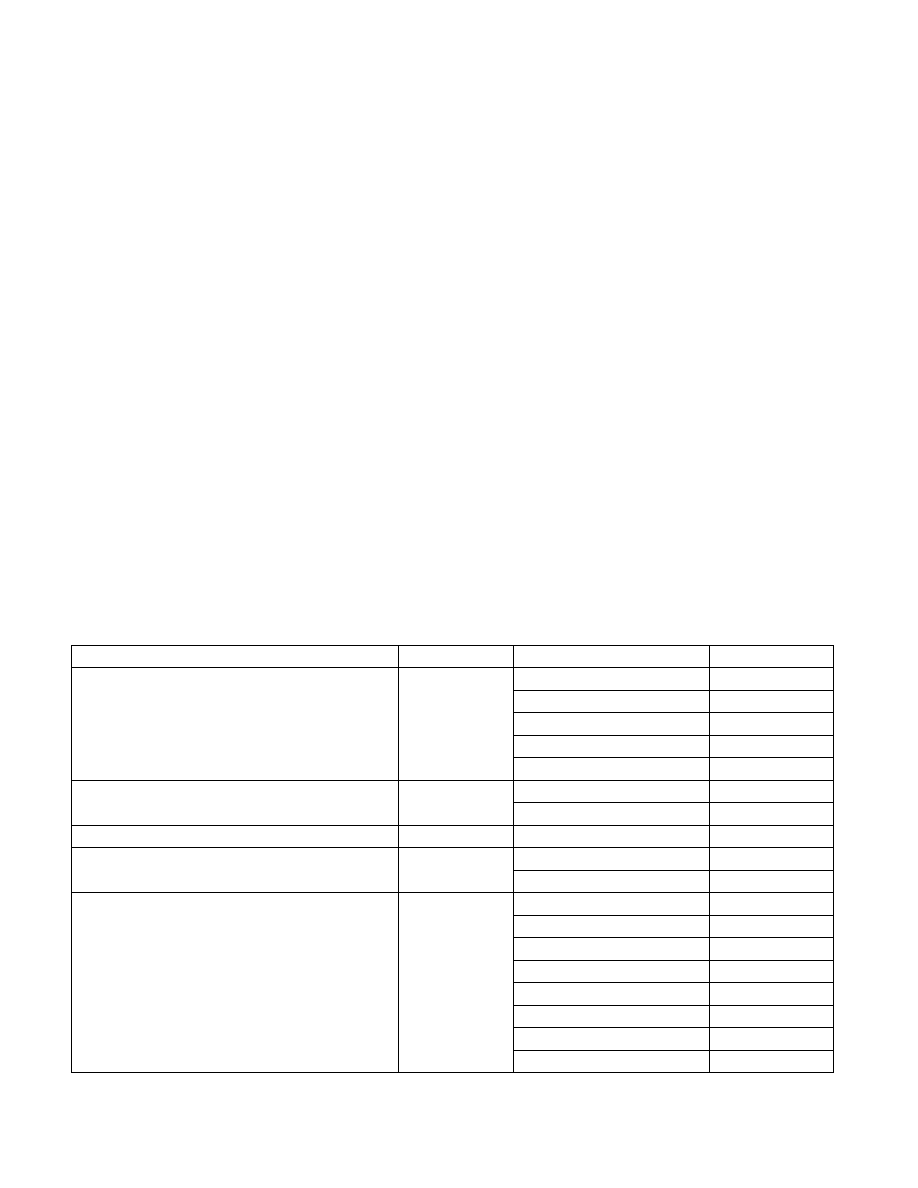

Table 18-19. Precise Events Supported by the Goldmont Microarchitecture

Event Name

Event Select

Sub-event

UMask

LD_BLOCKS

03H

DATA_UNKNOWN

01H

STORE_FORWARD

02H

4K_ALIAS

04H

UTLB_MISS

08H

ALL_BLOCK

10H

MISALIGN_MEM_REF

13H

LOAD_PAGE_SPLIT

02H

STORE_PAGE_SPLIT

04H

INST_RETIRED

C0H

ANY

00H

UOPS_RETITRED

C2H

ANY

00H

LD_SPLITSMS

01H

BR_INST_RETIRED

C4H

ALL_BRANCHES

00H

JCC

7EH

TAKEN_JCC

FEH

CALL

F9H

REL_CALL

FDH

IND_CALL

FBH

NON_RETURN_IND

EBH

FAR_BRANCH

BFH