Vol. 3B 18-31

PERFORMANCE MONITORING

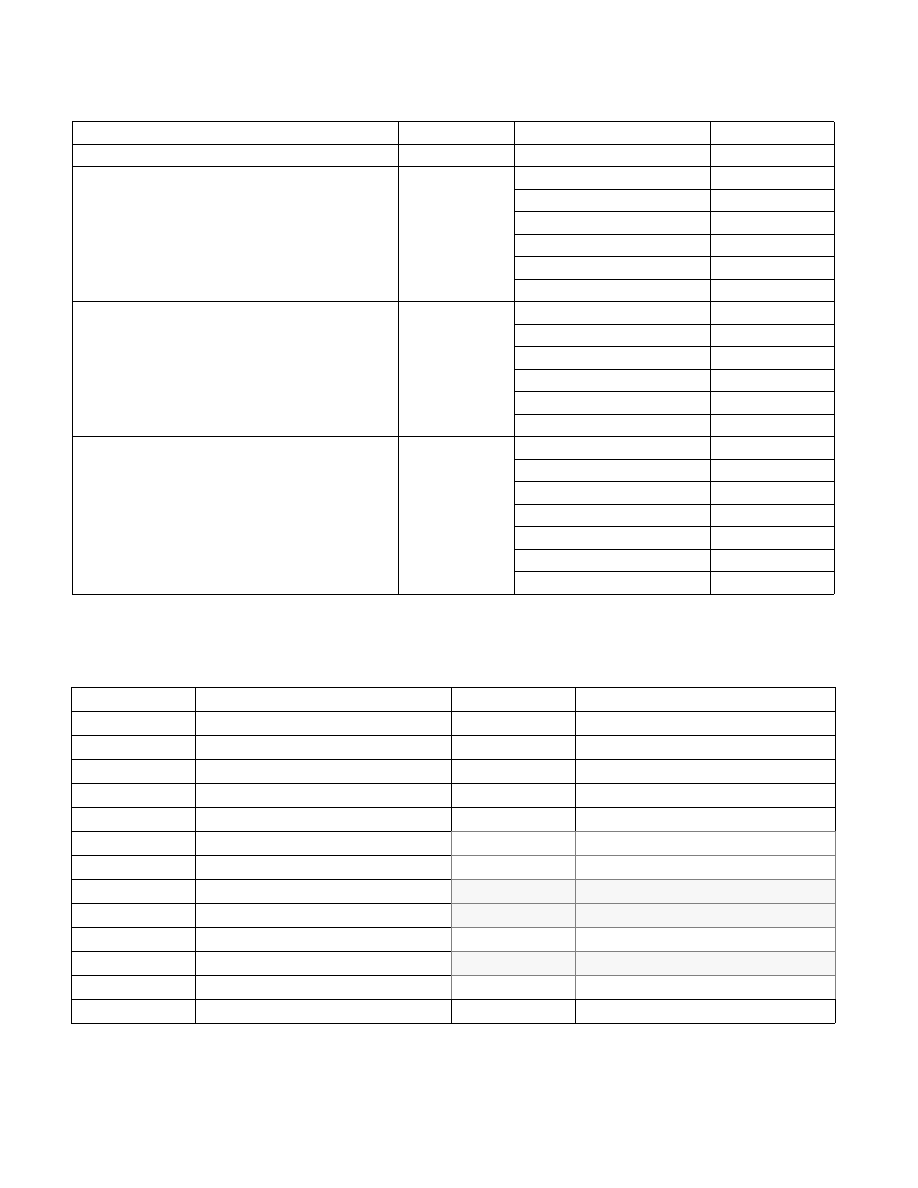

The PEBS record format supported by processors based on the Intel Silvermont microarchitecture is shown in

Table 18-13, and each field in the PEBS record is 64 bits long.

On Goldmont microarchitecture, all 64 bits of architectural registers are written into the PEBS record regardless of

processor mode.

RETURN

F7H

BR_MISP_RETIRED

C5H

ALL_BRANCHES

00H

JCC

7EH

TAKEN_JCC

FEH

IND_CALL

FBH

NON_RETURN_IND

EBH

RETURN

F7H

MEM_UOPS_RETIRED

D0H

ALL_LOADS

81H

ALL_STORES

82H

ALL

83H

DLTB_MISS_LOADS

11H

DLTB_MISS_STORES

12H

DLTB_MISS

13H

MEM_LOAD_UOPS_RETIRED

D1H

L1_HIT

01H

L2_HIT

02H

L1_MISS

08H

L2_MISS

10H

HITM

20H

WCB_HIT

40H

DRAM_HIT

80H

Table 18-20. PEBS Record Format for the Goldmont Microarchitecture

Byte Offset

Field

Byte Offset

Field

00H

R/EFLAGS

68H

R11

08H

R/EIP

70H

R12

10H

R/EAX

78H

R13

18H

R/EBX

80H

R14

20H

R/ECX

88H

R15

28H

R/EDX

90H

Applicable Counters

30H

R/ESI

98H

Data Linear Address

38H

R/EDI

A0H

Reserved

40H

R/EBP

A8H

Reserved

48H

R/ESP

B0H

EventingRIP

50H

R8

B8H

Reserved

58H

R9

C0H

TSC

60H

R10

Table 18-19. Precise Events Supported by the Goldmont Microarchitecture (Contd.)

Event Name

Event Select

Sub-event

UMask